首个64核 Zen 2 EPYC "Rome" 测试ID出现

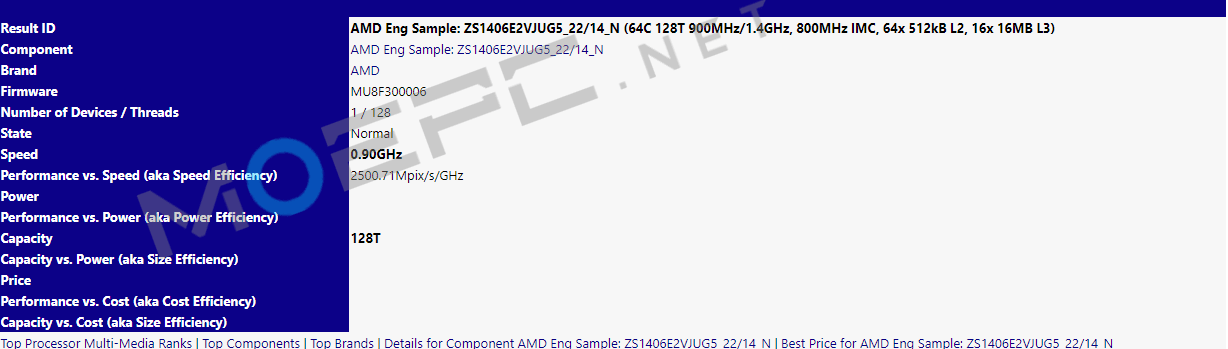

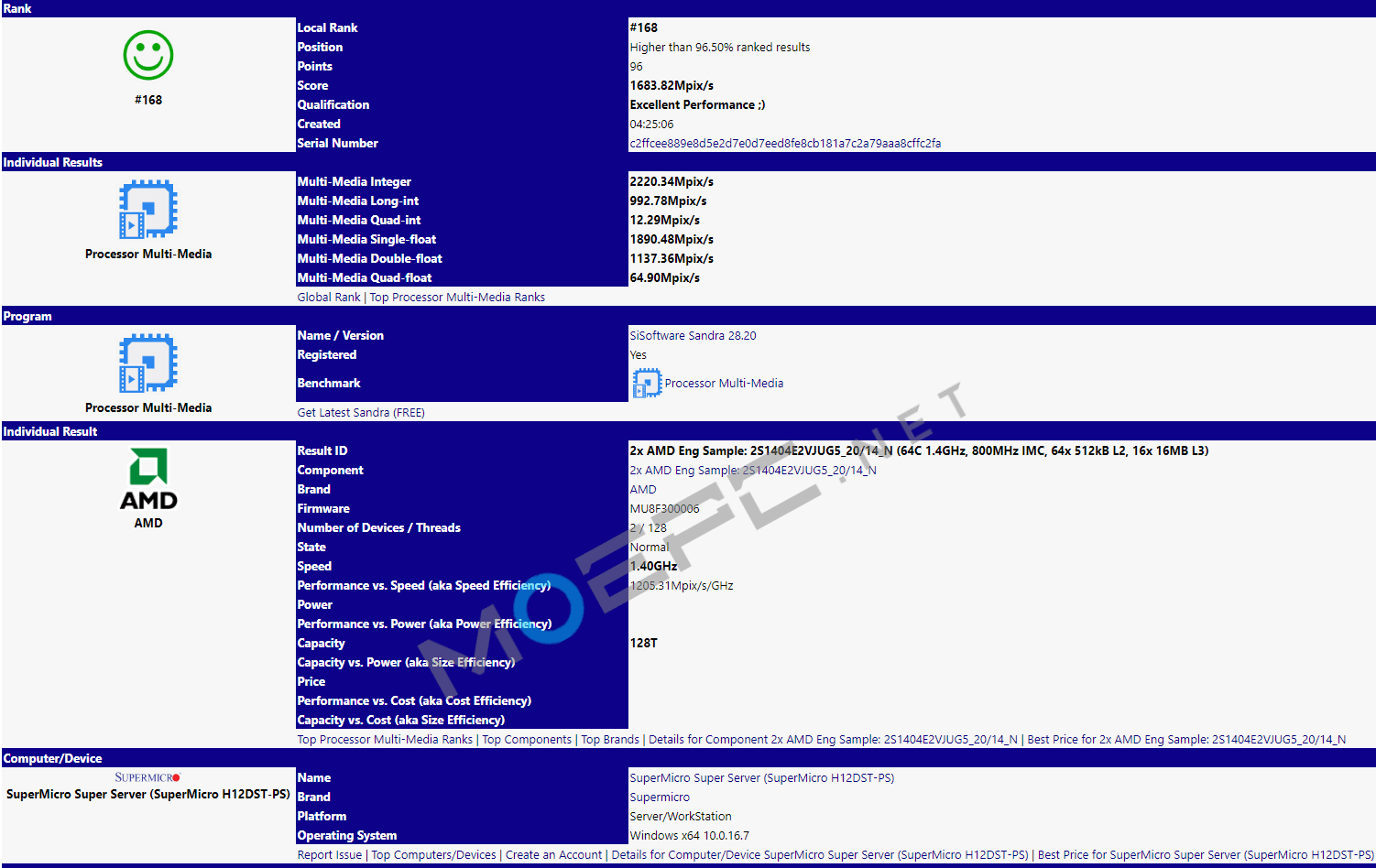

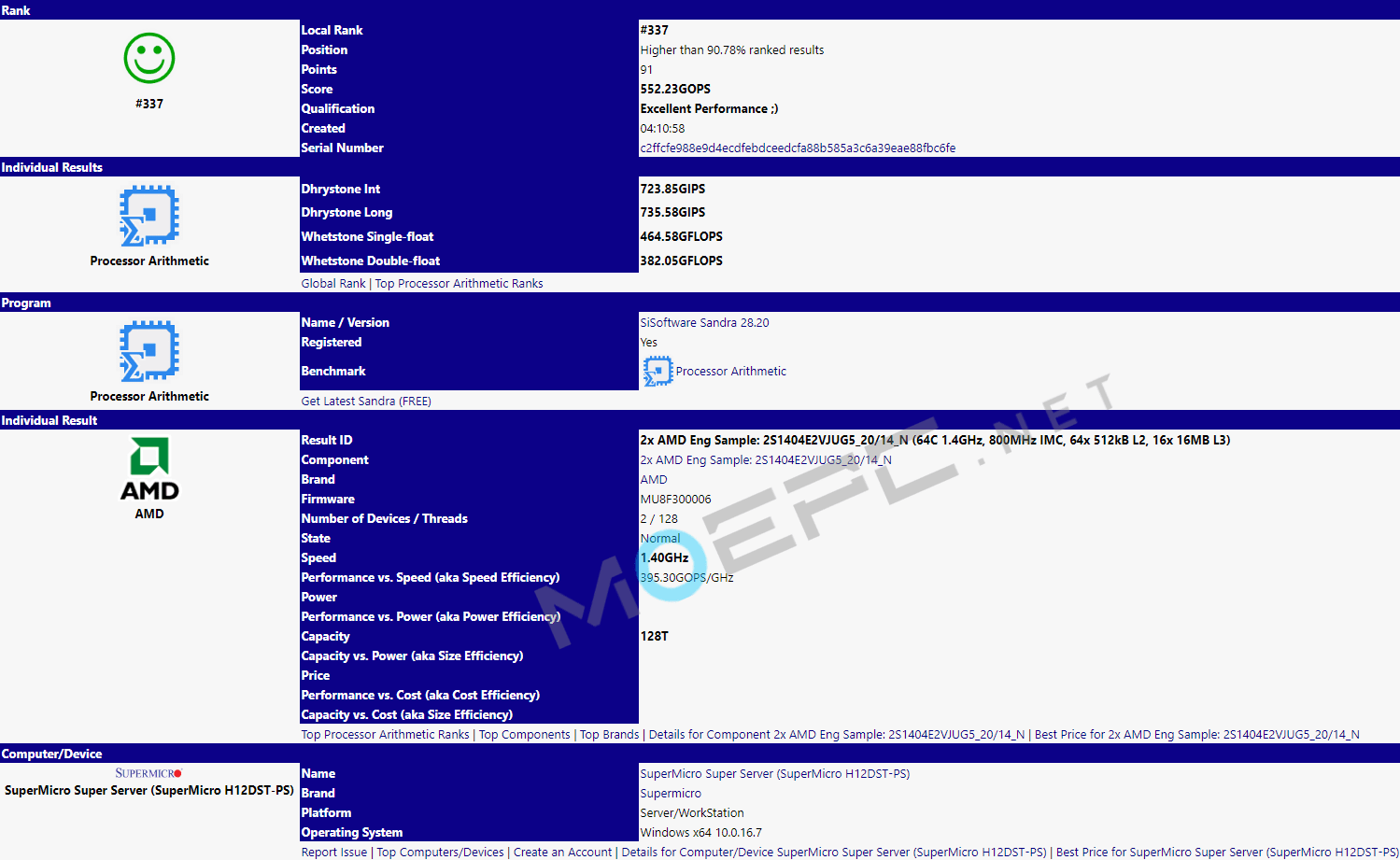

19/01/11更新:另一个Rome 的ID也出来了

这是一颗QS, 1.4/2.2GHz,64C/128T + 256M。

======18/11/23======

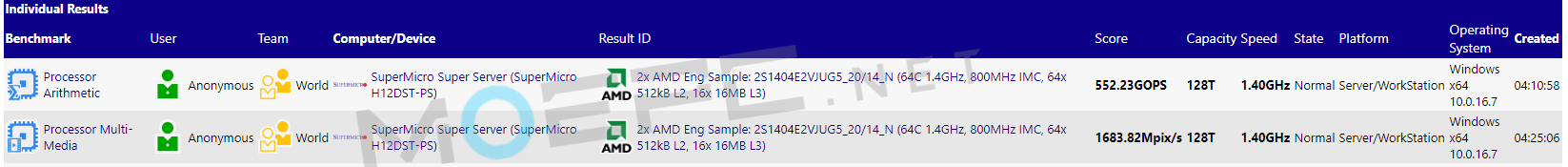

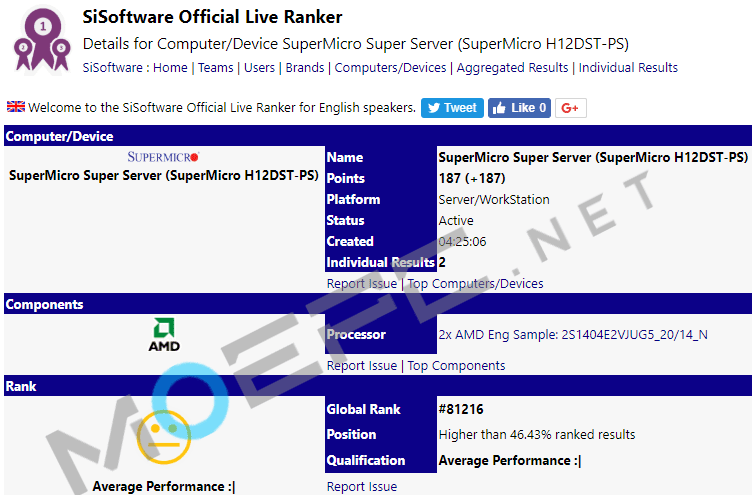

首个64核 EPYC2的测试ID出现在了Sisoft的数据库中。

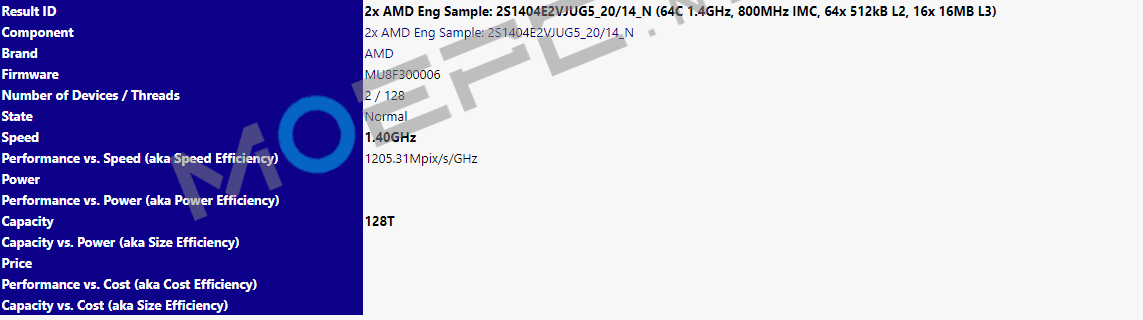

ID为:AMD Eng Sample: 2S1404E2VJUG5_20/14_N

ES1,1.4GHz基础频率,2.0GHz加速频率。

虽然显示的是双路,规格应该是单路的规格。

64C + 256MB L3。

其他的就没有什么值得解读的信息。

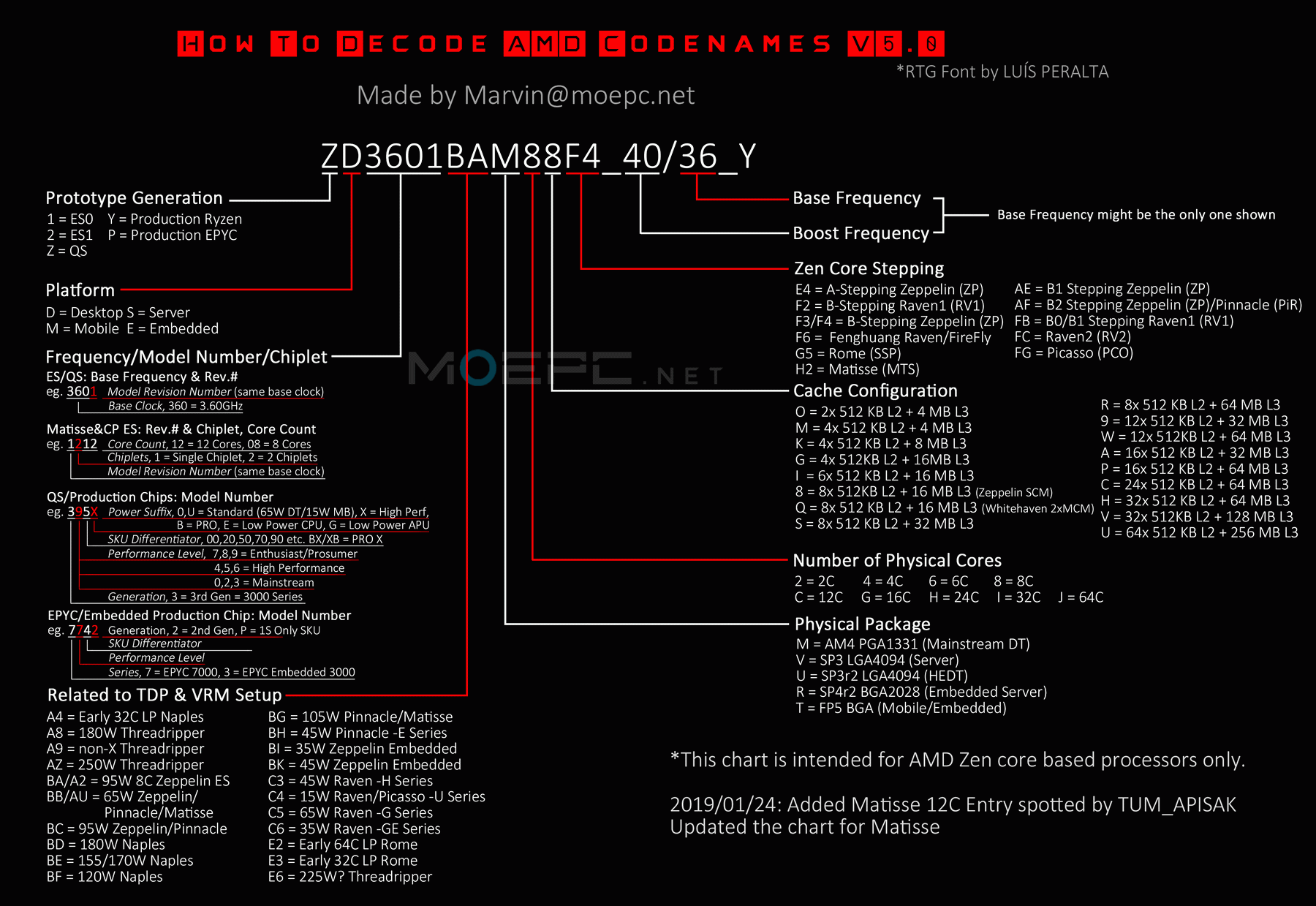

相关解读方式已经更新在这里:AMD 工程样品代码解读 V4.0 / How to Decode AMD Codenames V4.0 http://www.moepc.net/?post=5126

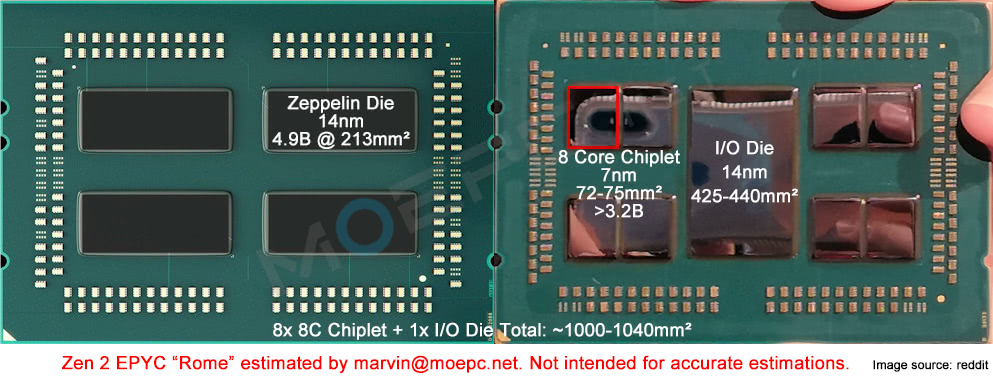

16x16MB L3的话,基本可以肯定是我之前说的单个Chiplet 2x 4C CCX。缓存翻倍到16MB。

除非检测的不正确。

但我之前得到的消息一直都说“Rome”是2x 4C CCX。

我之前已经做过了关于Zen2和EPYC2的分析,基本都被证明是正确的。想看的点击:

Zen 2架构:前端及浮点大幅加强,29% “IPC提升”?http://www.moepc.net/?post=5119#ZEN2

基于Zen2架构的EPYC,代号“Rome” http://www.moepc.net/?post=5119#ROME

N7 HPC密度、Zen2芯片面积相关 http://www.moepc.net/?post=5119#SIZE

“Rome”性能演示 http://www.moepc.net/?post=5119#PERF

早期的EPYC 样品频率都比较低。32核的Naples 早期ES基础频率也只有1.45GHz。相应的TDP和供电要求也比较低。

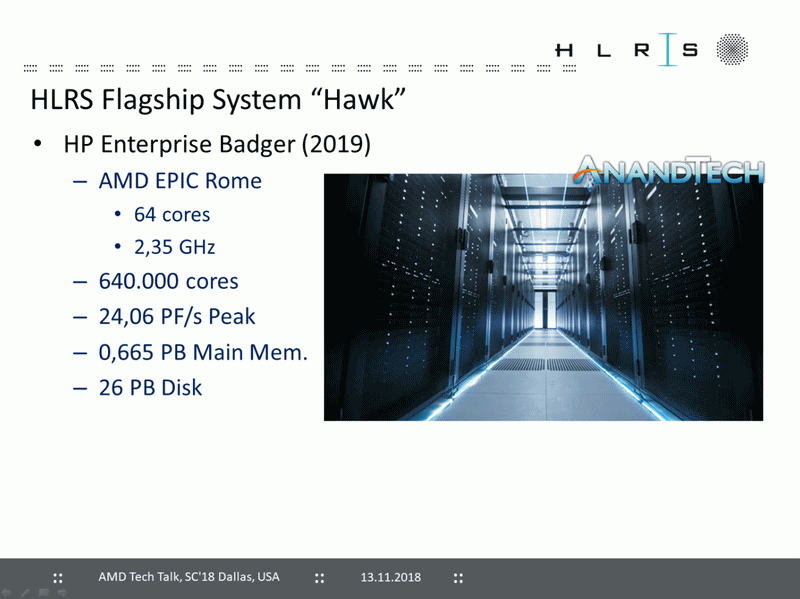

正式版当然会有更高的频率,给HAWK超算的Rome就达到了至少2.35GHz

关于HAWK超算的信息:http://www.moepc.net/?post=5119#HAWK

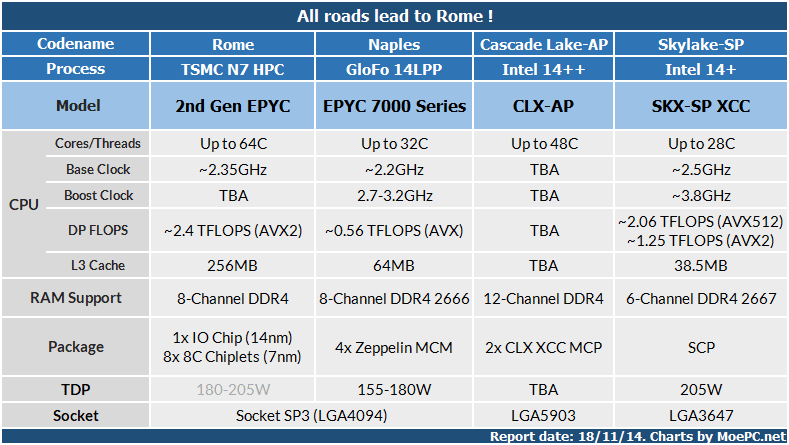

单路 2.35GHz的Rome 双精度性能 2.4 TFLOPS

单路 Skylake/Cascade-SP 最高2.1 TFLOPS,这是AVX-512的成绩。

图源:anandtech

单路Cascade-AP 有48C,性能会明显高于Cascade-SP,但目前不知道AVX2/AVX-512会降频到多少,还无法计算。【另外功耗爆炸】

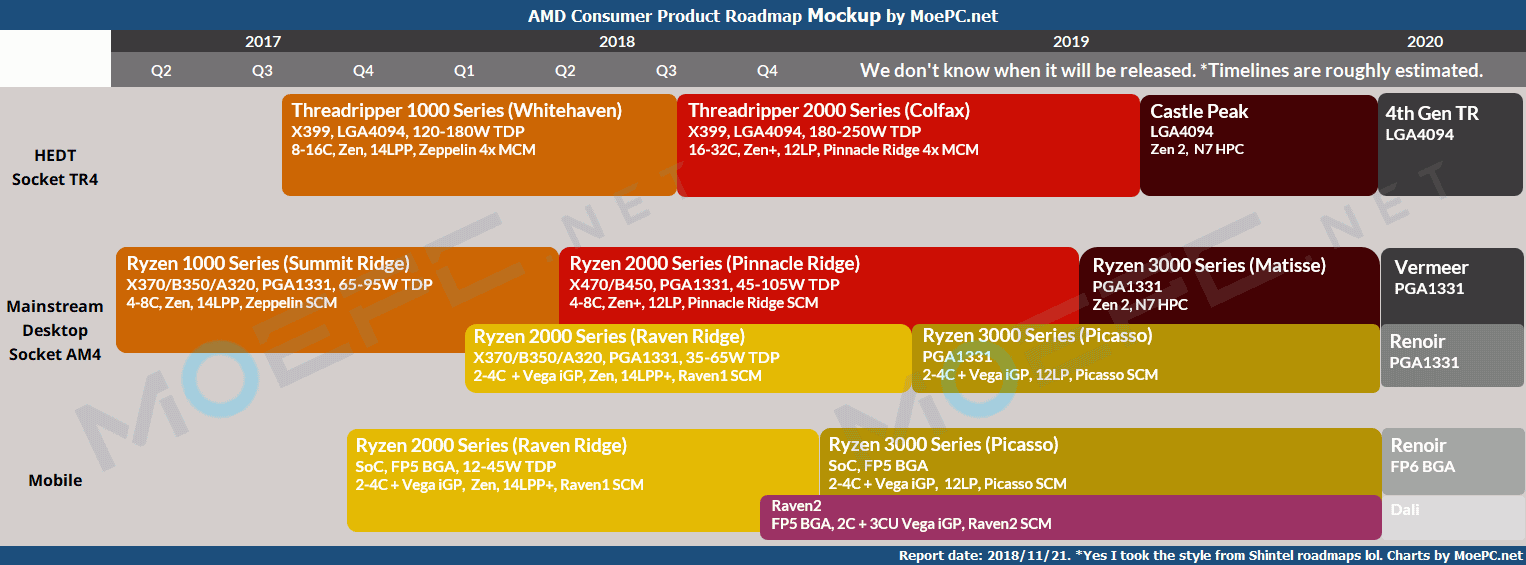

AMD将于2019年发布基于Zen 2 架构的 EPYC “Rome”, Ryzen 3000系列 “Matisse” 和Threadripper 3000 系列 “Castle Peak”。

来源:sisoft sandra database

via: TUM_APISAK

2个ccx内部互联怎么解决

victim cache的l3有翻倍的必要吗。。。

zen2 1个CCX 4核 有外挂一个i/o die ,游戏性能会不会开倒车了。。

CCX2CCX Latency&Bandwidth不知道会有何改进

目前还没有从其他渠道听说Zen 2的PCI-E通道数/多路互联带宽可现场配置的消息

加速频率只有2G的ES1 Rome就把双路8180M干翻了,有点猛呀,非常期待正式的消费级。

Zen 2单CCX 4C/8T,明白了。

国内PCEVA直接说单CCX 8C/16T,看来本镇瞎编还是很多的。

超能网孟宪瑞估算Zen 2芯片面积,感觉没常识,造谣yy能力强大。

@ayu:低能网日常造谣 偷别人文章还能搞错hhhhh

“Cascade-AP一个打俩”

殊不知Intel用的是双路,多了1.5倍核心。

至于4C CCX其实我很早之前就收到消息了的。

@剧毒术士马文:马文有空能不能讲解下ZEN+ ZEN 内存超频 小参设置的知识

比如Trfc值 soc vddnb , 我找了很多网站都找不到超内存详细攻略

@ZEN+超Bdie:AMD Ryzen 内存超频:频率 vs 时序

http://www.moepc.net/?post=2472

这个是去年的文章

时序手动优化比较麻烦。。。