SiFive发布P550/P270 RISC-V架构核,Intel 7nm制程平台2022年登场

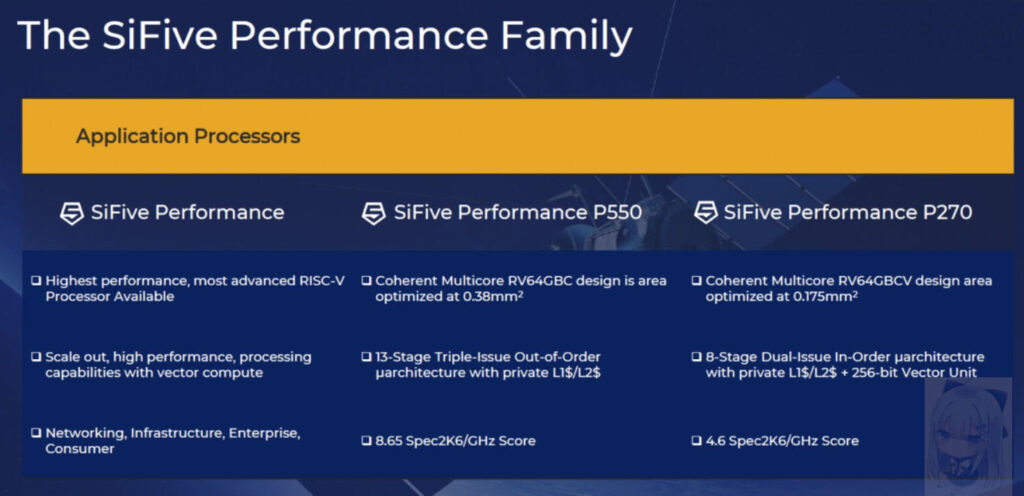

SiFive刚刚发布了最新的RISC-V架构核心P550和P270。其中P550为当前最高性能的RISC-V处理器核心,而P270则是SiFive首颗能在Linux上完整支持RISC-V Vector v1.0 rc拓展指令集(RV64V)的处理器核。

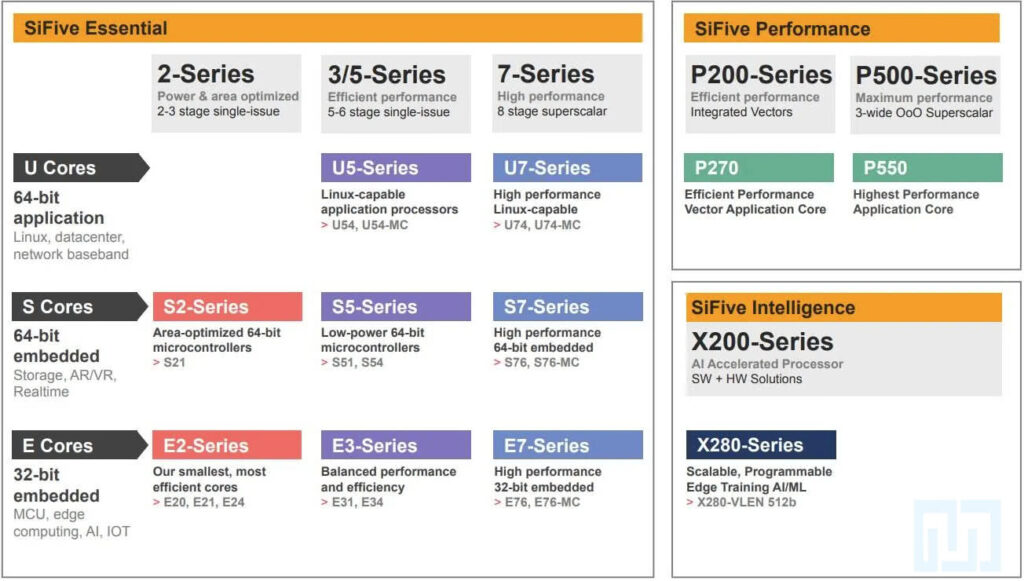

SiFive目前的产品规划。原本是最高性能的U8x、U/S/E7x系列,中等性能的U/S5x、E3x系列,以及面向低端面积优化的S/E2x系列。U系列可以运行Linux(Cortex-A),S系列面向存储,AR/VR等实时处理(Cortex-R),E系列面向嵌入式(Cortex-M),面向AI加速的X200系列比较特殊,支持RV-V 512bit Vector。这次的P550/P270均为U8x/U7x改进架构得来。

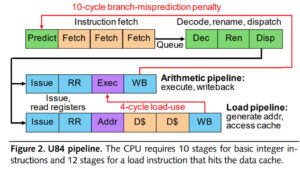

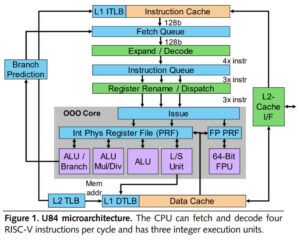

距离上次SiFive公开高性能核心已经快三年了,上次公开的还是2019年的U84,号称达到Cortex A72级别性能。U87没有公布太多细节,而且实际公开的情况也没有在出货所以不算。

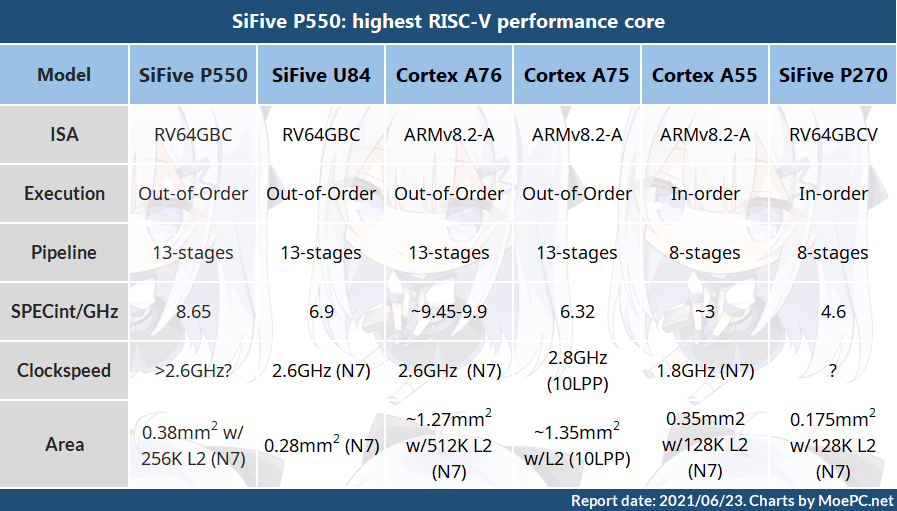

这次发布的P550支持RV64GBC(RV64IMAFDCB)指令集,13级 3-issue 流水线(和U84/A76/A75相同),乱序执行,32+32KB L1。在TSMC N7工艺下搭配256KB L2时的面积为0.38mm2。四核心丛集可搭配最高4MB L3。

流水线详细并没有公开太多,但scalar pipeline方面个人认为应该还是基于U84改进的。

P550无论从流水线长度以及性能上更类似与ARM的Cortex-A7x系列。官方在比较中用到的是Cortex A75:四核心P550 core complex的面积和单核Cortex A75的面积相近,PPA高很多。在这里官方并没有提到使用的node和是否iso-node比较。

当然我们可以拿现有数据来比。Krin 980上Cortex-A76(32+32K L1, 512K L2)的面积大概在1.27mm2,同样是TSMC N7工艺。如果非要拿A75比的话就没有iso-node了,S845的A75(10LPP w/L2)面积大概在1.35mm2。4核心P550+1MB L2的话算下来需要1.52mm2,比单核A76大了0.25mm2,比A75大了0.17mm2,PPA优势非常明显,P550单核面积和A55差不多了。(注:官方宣称P550相当于CortexA75 三倍的PPA)

性能方面官方宣称的是SPECint2006测试性能8.65/GHz,大概在A75和A76之间,比19年的U84高出25%。但是这里的结果首先无法代表所有频率下的性能,且性能并不是随着频率而线性增长,更不要提memory subsystem的配置不同也会影响性能。所以在这里做出的projection只能当个大概看看。

作为baseline的频率为2.6GHz,因为U84在N7工艺下能够达到的最高频率就是2.6GHz,P550的流水长度并没有增加,因此也使用2.6GHz作为target。iso-node使用了Kirin 980(9.9/GHz,2.6GHz)和S855(9.45/GHz,2.84GHz)当然,这个projection 仅供参考,仅供参考,仅供参考。2.6GHz P550 理论上性能低于A76,实际性能应该会在A76和A75之间,单线程高于A75。官方对标的是A75。

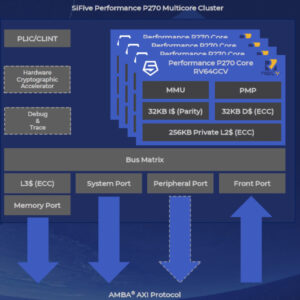

另一颗P270核心则更类似于Cortex-A55/A510。P270支持RV64GBCV(RV64IMAFDCBV)指令集,通过RV-V拓展支持256bit vector运算(VLEN = 256. DLEN = 128 (datapath width). ELEN = 64 (datatypes))。它只有8级 2-issue的流水(与A55相同),顺序执行,32+32KB L1。TSMC N7工艺下128KB L2配置面积为0.175mm2,是A55 0.35mm2的一半不到。

性能指标上SPECint06达到了4.6/GHz(RV堆integer的效率的确会比ARM高很多…),A55大概在3左右,比A55大概高出50%。频率情况因为没有其他参考数据,baseline就设定为与A55相同的1.8GHz。同样的,这个projection仅供参考。其他性能方面,P270达到了5.75 CoreMarks/MHz,Dhrystone 3.25DMIPS/MHz。

除开这两款RISC-V架构的发布之外,Intel 也宣布将会采用SiFive的P550核心设计自己的芯片。

原话:

“We are pleased to be a lead development partner with SiFive to showcase to mutual customers the impressive performance of their P550 on our 7nm Horse Creek platform,” said Amber Huffman, Intel Fellow and CTO of IP engineering group at Intel. “By combining Intel’s leading-edge interface IP such as DDR and PCIe with SiFive’s highest performance processor, Horse Creek will provide a valuable and expandable development vehicle for cutting-edge RISC-V applications.”

Intel的RISC-V平台代号为Horse Creek,将采用P550核心,使用自家7nm制程制造。同时还将搭配Intel 自家的DDR和PCIe IP等。结合最近Intel 收购SiFive的消息,可以看出Horse Creek 类似于Intel Foundry Services(IFS)的reference design。Horse Creek预计于2022年完成。

当然SiFive 目前还是在独立运作的,所以在台积电和三星也都有设计。OpenFive Chiplet Refernce Platform将采用TSMC N5制造。同时SiFive的R-V AI SOC开发平台也会跟三星合作。

area的数据大差不差,性能数据差太多啦。a55 n7 spec2k6有4.3,iso node的a76 spec2k6突破10了

另:a75 n7 512L2的area在1个mm2左右

毕竟都是napkin math

这ppa吊打arm啊

这让nvidia怎么吹