芯片架构正为了适应大数据要求而改变

业界共同的愿景是开发一款人工智能(AI)处理器,它可为神经网络处理训练与推理等任务,甚至可能出现一些新的自我学习技术;这种AI处理器还必须能透过大规模的平行化方式提供强大的性能,同时具有高功效且易于编程…

由亚马逊(Amazon)、Google和Facebook等网络巨擘所收集的大量数据集,正推动处理这些巨量数据的新芯片复兴。预计在六月底的年度计算机架构大会上将亮相其中两项最新成果。

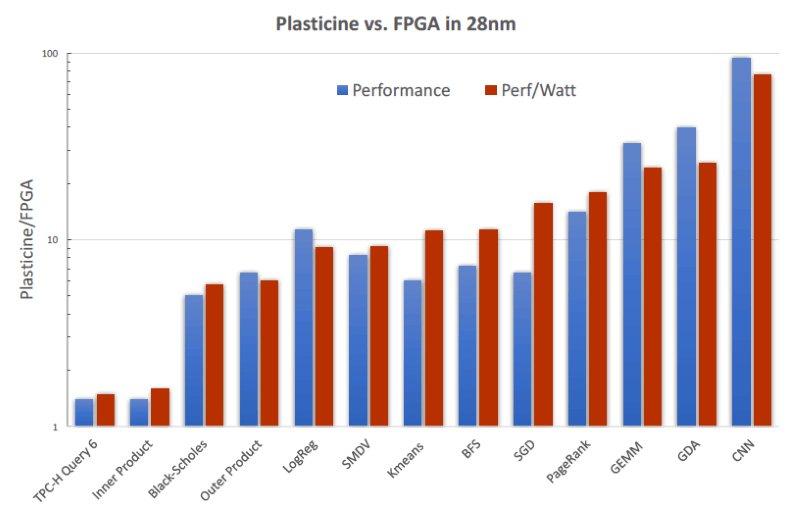

斯坦福大学(Stanford University)的研究人员将介绍一种可重配置处理器??Plasticine,它可支持比FPGA更高近100倍的每瓦特性能,同时也更易于编程。此外,Nvidia的两名资深设计人员定义了一款推理处理器,可提供较现有组件更高2倍性能与能源效率。

这些芯片象征着这项任务的冰山一角。过去一年来,英特尔(Intel)收购了三家机器学习创业公司。而其竞争对手??三星(Samsung)则连手Dell EMC投资英国公司Graphcore,这是该领域的六家独立新创公司之一。

Nvidia正致力于推动其GPU作为神经网络训练引擎的销售。同时,该公司也正调整其芯片架构,使其得以更有效地处理这些任务。

Google则声称其庞大的x86 CPU丛集以及Nvidia的GPU均不足以胜任这项处理任务。因此,Google推出了自家的两款加速器版本??Tensor处理器(TPU)。

Graphcore首席执行官Nigel Toon说:“如今正是‘计算2.0’(Compute 2.0)的时代,它象征着一个全新的运算世界。Google最终将使用以TPU为基础的机架结构,几乎不使用任何CPU,因为它有98%的营收都来自搜寻??这正是机器学习的理想应用。”

最终,机器学习芯片将出现在广泛的嵌入式系统中。以汽车每年卖出1,800万辆和服务器约1,000万套的年销售量来看,Toon说:“自动驾驶车应用可望为这项技术带来一个比云端更大的市场,而且是一个以往从未存在过的市场。”

如今业界共同的愿景是开发一款人工智能(AI)处理器,它可为神经网络处理训练与推理等任务,甚至可能出现一些新的自我学习技术。这种AI处理器还必须能透过大规模的平行化方式提供强大的性能,同时具有高功效且易于编程。

即使是这项开发任务的基本数学也引发热烈讨论。Toon认为,16位浮点乘法与32位累加运算的组合,能够带来优化精确度以及最小误差。

这正是Nvidia Volta架构导入的Tensor核心所使用的途径,同时也是Graphcore将在今年10月出样给早期合作伙伴的高阶芯片。该新创公司正专注于开发一款采用新内存与互连的大型芯片,该芯片并可外接至各种单元与丛集。

后多核心时代的灵活性

由Kunle Olukotun带领的斯坦福大学研究团队也有类似的目标,不过,他们采取了一条与Plasticine不一样的道路。

Olukotun说:“多核心时代即将结束……我们正处于一个现代应用程序(app)改变运算模式的时代。”Olukotun曾经协助一家新创公司率先打造出多核心设计,该技术最终成为Oracle基于Sparc处理器的一部份。

“对于机器学习的统计模型,真正需要的运算方式与古典的确定性运算途径截然不同,所以这将带来一个真正的机会。”

如同英国布里斯托的竞争对手Graphcore一样,斯坦福大学研究团队摒弃了共享一致的快取等传统思维。斯坦福大学数据科学计划执行总监Stephen Eglash认为,Plasticine“最令人兴奋之处在于硬件可在运行时重新配置,为特定计算方式实现优化。”

Olukotun说:“我们的目标在于让拥有专业知识的任何人都能建立可生产的机器学习系统,而不一定得由机器学习或硬件领域的专家来做。”

为了实现这一目标,斯坦福大学定义了一种新的语言Spatial,可将算法的各部份映像至平行处理器的各部份。Olukotun说:“我们拥有完整的编译程序流程,从高层级的Tensor Flow架构到硬件呈现……事实上,它具有比FPGA更高10倍每瓦特性能,也更易于编程100倍。”

Spatial类似于Nvidia的Cuda GPU编程语言,但应该更易于使用。它能将诸如分散/收集或MapReduce等功能映像至硬件中的外显内存阶层架构,经由DRAM和SRAM实现串流数据集。

因此,Pasticine处理器“是一项软件至上的计划,”Olukotun说。

Eglash认为在物联网的边缘节点正需要这样的技术。“我们所产生的数据将会比传送至云端的更庞大,所以必须采用一些分布式的本地运算。”

短期来看,机器学习将为智能型手机带来“超级个性化”,针对使用者的喜好自动量身打造。别再为密码和指纹伤脑筋了。Eglash说:“你的手机可能在几秒内就知道你是不是本尊。”

在工业物联网(IIoT),推理任务已经被分配至网关了。GE Digital云端工程主管Darren Haas说,“我们所打造的一切都可以被划分成较小的设备,甚至是Raspberry Pi …我们在云端建立了大规模的模型,并使其得以在边缘执行于轻量级硬件上。”

斯坦福大学的Plasticine架构

斯坦福大学的Plasticine是一种全新的架构,可能是Graphcore等新创公司将会采用的技术。它充份利用了平行模式和高层级抽象,以撷取有关数据位置、内存存取模式和控制流程等细节,从而在“一系列的密集与稀疏应用上进行操作”。

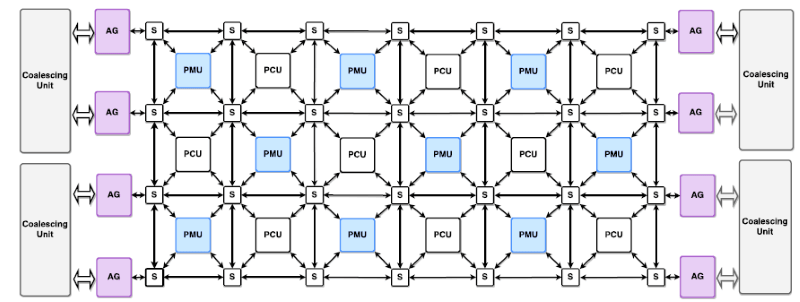

在该芯片核心采用16×8的交错式图形运算单元(PCU)数组与图形内存单元(PMU),透过3个互连信道利用3种控制协议进行连接。这款尺寸为113mm2的芯片采用Spatial将应用映像至数组上;相较于采用类似28nm工艺打造的FPGA,该芯片可提供更高95倍的性能以及高达77倍的每瓦性能。

Plasticine在1GHz频率频率下的功耗高达49W,支持12.3TFlops的峰值浮点运算性能,以及16 MB的芯片容量。

PCU是执行巢状模式之可重配置SIMD功能单元的多级管线。PMU使用库存的缓存器内存和专用寻址逻辑与地址译码器。

采用16×8的PCU与PMU数组,以及地址产生器和交换盒

这些主单元和其他周边组件透过字级纯量、多字符向量和位级控制互连进行连接,且全部都采用相同的拓扑结构。各个连接都采用分布式的分层控制机制,以尽可能减少使用同步单元,从而实现序列、流水线或串流的执行。

该途径简化了编译程序映射并可提高执行效率。“每个Plasticine组件均用于映像应用的特定部份:本地地址计算在PMU中完成,DRAM地址运算发生在DRAM地址管理单元,其余的数据运算则在PCU中进行。”

Olukotun解释说:“本质上,它是一组高度库存的内存,支持专用地址单元产生附近的地址。只需执行计算,即可让内存在正确的时间将数据串流至运算单元,而无需解译指令。”

该芯片采用四个DDR信道外接DRAM,并进行缓冲和管理,以尽可能减少芯片外处理。

Olukotun说:“许多机器学习都专注于建置卷积神经网络(CNN),但我们的目标是打造更灵活且涵盖稀不断变化中的疏密集算法,让开发人员可以将其设计想法传达给硬件。”

研究人员采用周期精确仿真来合成设计的RTL,为线性代数、机器学习、数据分析与图形分析等任务产生基准。他说:“我们希望这些设计概念能直接用于芯片上,并计划在6到18个月内进行芯片设计。”

Plasticine与英特尔28nm Stratix-V的性能比较 (来源:Stanford)

Plasticine与英特尔28nm Stratix-V的性能比较 (来源:Stanford)

Nvidia研究人员打造稀疏推理引擎

另一组由9名研究人员组成的研究团队(其中有7人来自Nvidia)将介绍稀疏卷积神经网络(SCNN)推理加速器。该研究团队包括资深的微处理器设计人员Joel Emer(曾协助定义同步多线程),以及Nvdia首席科学家William Dally。

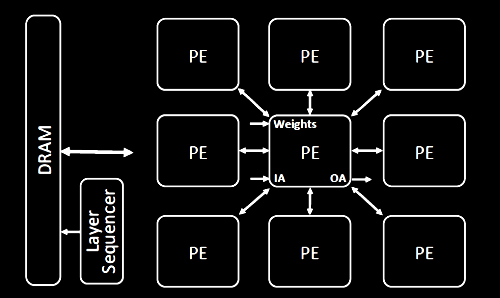

相较于同级配置的密集CNN加速器,SCNN可提供更高2.7倍的性能和2.3倍的能源效率。该芯片采取较以往的研究更先进的途径,可消除无关紧要的数学运算,并专注于以最高效的方法处理CNN权重与启动。

此外,它采用了一种新的数据流,可在压缩编码过程中保持稀疏权重与启动,从而避免不必要的数据传输以及减少储存的需求。此外,“SCNN数据流有助于将这些权重与启动有效地传递到乘法器数组,并在此广泛重复使用。”

该途径可让“较大CNN的所有操作量保留在各层间的芯片缓冲区,完全不必使用大规模网络所需的高成本跨层DRAM参考资源。”

SCNN使用处理元素(PE)数组,处理权重以及输入/输出启动 (来源:Nvidia)

该芯片的处理元素(PE)采用支持权重和启动向量的乘法器数组。该芯片采用16nm工艺技术,将64个PE与16个乘法器封装于7.4mm2模块中,使其尺寸略大于类似的密集CNN加速器。

该论文并比较了SCNN与其他研究中的芯片。然而,Dally猜测这款芯片“比商用推理加速器的效率更高,因为它利用的是稀疏设计途径。”

如同Plasticine一样,目前的研究成果是以仿真为基础,尚未制造芯片。Dally说:“我们正为这款设计进行布局以及时序收敛。”

Nvidia尚未宣布商用化SCNN技术的任何计划,但在研究论中指出,“我们正持续在这个领域的研发工作。”

原作者:Rick Merritt

编译:Susan Hong

via:eetimes taiwan