PCI Express准备升级至5.0 – 32G

PCI SIG在年度会议上宣布,最快在2019年就会推出可提供32GT/s的第五代(Gen 5)PCI Express(PCIe)规格,为铜缆互连技术升级带来另一个新的里程碑。不过,PCI SIG在这次会议上的主要任务还是完成16GT/s传输速率的第四代(Gen 4)规格。

这个消息象征广泛使用的计算机互连接口速度将会显著增加。事实上,随着PC市场持续放缓,PCI Express已经原地踏步好几年了。而今,PCI Express Gen 5即将面世的消息,刚好就是CCIX、GenZ和OpenCAPI等各种开放互连标准迅速兴起而可能让这一领域变得更为分散的时机。

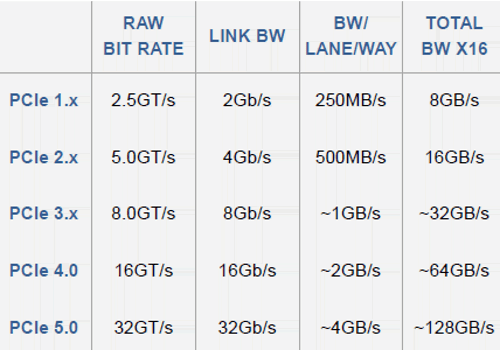

PCIe Gen 5将使用128/130位编码,可在16个4GB/s的通道中提供高达128GB/s的速度。预计它将为高阶图像处理器(GPU)、机器学习(machine learning)加速器,以及以太网络(Ethernet)和Infiniband卡提供执行速度达400GB/s的互连传输。

PCI SIG的成员已经为PCIe Gen5准备好0.3版架构规格了。该小组目前正针对Gen 4标准的0.9版进行最终审查。

32G新规格的提出,正值兴起中的大型数据中心持续推动串行解串器(serdes)互连的速率提升到更高的56Gbit/s之际。

PCI SIG总裁Al Yanes表示,“我们可以利用其它标准,从业界现有的大量PHY进行开发。Gen 4的许多规格与成果都可以沿用到下一代,这让Gen 5的任务更容易。工作小组对于完成规格和时间进度都很有信心。”

工程师尚未确定新规格是否会对PCI Express的适用范围施加新的限制,或是要求比FR4成本更高的电路板材料。但他们已经确定的是,PCIe Gen 5将与PCI SIG在过去25年来开发的规格一样兼容前几代的规格。

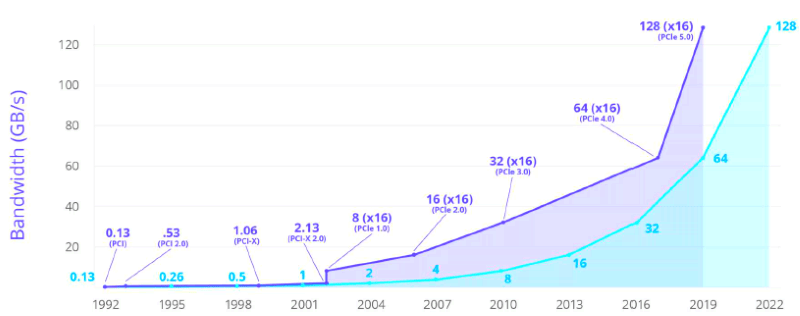

*经过2010~2017年间的沉寂后,PCI SIG正加速其发展蓝图 (来源:PCI SIG) *

IBM研究员Brad McCredie表示,随着追逐摩尔定律的代价变得更加昂贵,为了满足对于系统性能的要求,PCIe Gen 5象征业界在快速I/O方面的工作正加速进展。这位资深的微处理器工程师正致力于Power 9,计划在今年稍晚让Power 9成为首款使用PCIe Gen 4的商用CPU。

业界至今“已经连续使用PCIe Gen 3长达7年了,我认为…我们必须加快Gen 4的进程,”McCredie说:“我们需要利用这些高性能的总线与加速器通讯,从而提供更高的成本效益。”

他补充说:“预计Gen 4的主流应用将在2019年以后才会出现,但如果PCI SIG持续推动进展,我们将在2020年实现第10版Gen 5标准。”

McCredie并不愿对于普遍预期铜缆互连终结的看法加以预测。然而,他表示希望Gen 4连接器仍能用于32GT/s的传输速率,而且在Gen 5以后也可能持续更新铜缆PCIe规格。

他说:“从2005年的Power 6开始,我们就一直在说这是最后一版了。但是,每一次,I/O工程师都再度摩拳擦掌,让互连速率继续倍增。”

同时,McCredie说,IBM是其他可供选择的开放互连组织(如CCIX)成员之一,“我们正在评估所有的开放附加功能。”

虽然完成16G规格的时间比预期更长,但有几家公司正着手先行推出使用该规格的产品了。Yanes说,其中有十几家公司已经将装置带到最近举行的Gen 4研讨会上去进行测试了。

在去年的PCI SIG上,包括Cadence、PLDA和Synopsys等几家公司就已经展示了PCI 4.0的物理层(PHY)、控制器、交换器以及其他IP模块了。他们还展示了采用PCIe 4.0的100Gbit/s Infiniband交换器芯片等各种可用芯片、板卡与背板。

在今年的会议期间,Cadence和Synopsys将发表用于多个市场的Gen 4 IP,尤其是车用领域。是德科技(Keysight)和Teledyne LeCroy将展示Gen 4就绪的测试仪;NEC则将介绍一款可桥接PCIe外围设备和以太网络的新式芯片。

IBM与Mellanox、赛灵思(Xilinx)等合作伙伴则计划在今年稍晚推出支持PCIe Gen 4网络和加速卡的Power 9。此次的活动预计还将包括共同推动Power 9系统成为IBM Open Power Initiative计划一部份的其他公司。 McCredie说:“PCIe Gen 4总线来得很快,但在实际的建置上也没有太多的意外??我们已经建立了能实现完整互连的理想产品模型。”

PCI Express的演进

随着带宽数字持续增加,PCI Express正不断演进中

IBM期望PCIe总线及其自家的OpenCAPI互连能够支持各种网络、储存卡和加速器。有趣的是,McCredie看好英特尔的3D XPoint内存作为储存级内存的发展潜力,认为它能够透过OpenCAPI进行同步存取,从而成为介于DRAM和闪存之间的新型内存。

“我认为3DXP可望成为一种极具颠覆性的技术,”他说。“用于同步存取,它绝对够快了…但我不想为了这种3DXP技术再更新DIMM插槽了。”

截至目前为止,在OpenCAPI上使用3DXP还只是个概念,他指出,“我们尚未与其他人在这方面形成共识。”

相较于128GB/s的PCIe Gen 4,OpenCAPI的带宽峰值高达150GB/s。IBM希望能藉此吸引合作伙伴加入其围绕Power 9打造的生态环境。

在中国不断成长的电子产业培养合作伙伴方面,IBM一直动作不断。它已经启动了一个发展蓝图,其中包括现正进行中的Power 9,以及预计在未来三年的Power 10设计。

McCredie表示,IBM最近宣布在5nm纳米片(nanosheet)晶体管上的工作,可望为日后的发展铺路。他强调,“现在Power 11也拥有未来所需要的工艺技术了!”

(参考原文:PCI Express Preps Shift to 32G,by Rick Merritt)

via:http://www.eettaiwan.com/news/article/20170706NT31-PCIe-preps-shift-to-32G

PCIE4都还没见到商用,又放PCIE5出来,怕是PCIE4

@星星酱:规范肯定是早于商用的,你看HDMI和DP的版本都到哪里了,现在显示器依然只买得到DP1.2的。单线缆5K只能依赖在雷电接口上同时开两条DP1.2链路。