Intel展示10nm晶圆,确认下代FPGA "Falcon Mesa"将采用10nm制程【Anandtech】

Intel日前在北京精尖制造日上展示了自家10nm晶圆,证明“手上已经有10nm晶圆”。Intel称该晶圆为Cortex A75的10nm测试芯片,主频超过3.3GHz,每MHz功耗250uW。

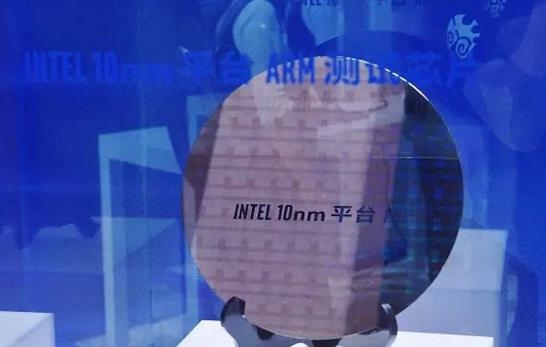

10nm ARM晶圆

10nm CNL晶圆

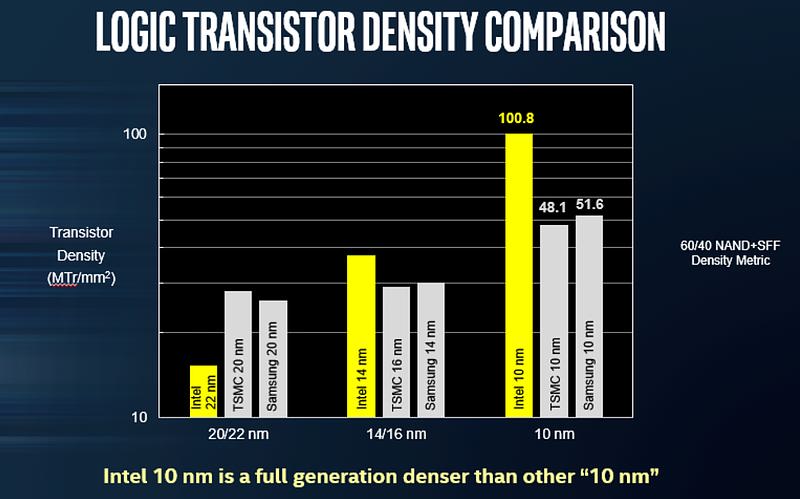

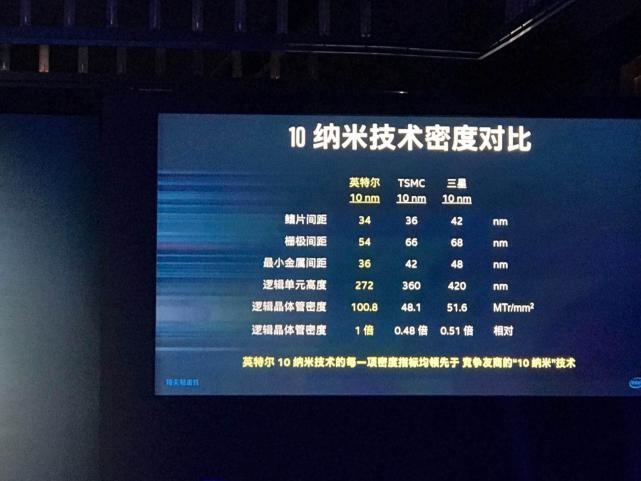

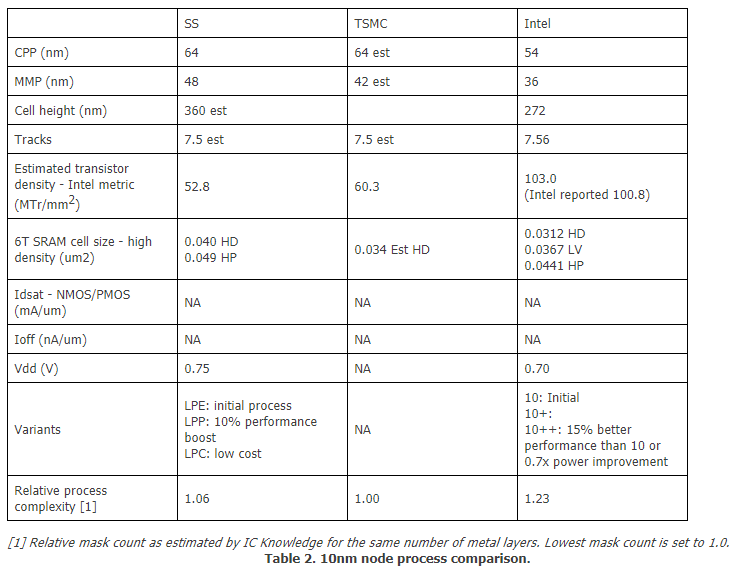

目前台积电和三星都在出货自己的“10nm”制程,Intel称自家的10nm晶体管和沟道更紧凑,密度达到其他代工厂的2倍。台积电10nm的Kirin 970为5500万晶体管/mm2,而Intel称自家10nm达到了1亿+晶体管/mm2(并采用新的晶体管计数方式)。

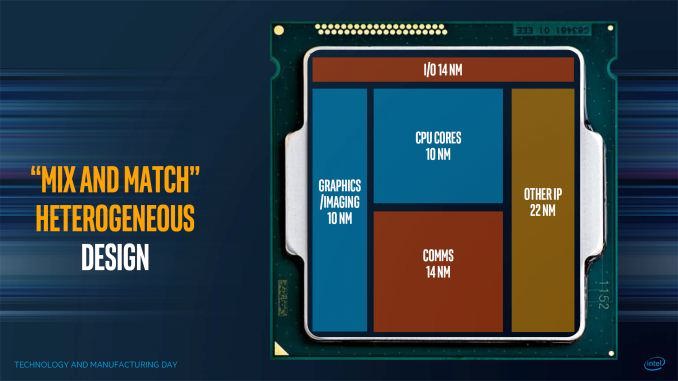

Intel声称10nm比14nm性能高25%,功耗降低45%,然而并没有明说是14还是14+、14++。而10nm优化版10++可以选择在10nm基础上性能提升15%或者降低30%功耗。Intel的定制代工业务从10nm开始,提供两种设计平台:10GP(General Purpose)以及10HPM(High Performance Mobile),还有包括ARM库、POP套件及Turnkey服务的经验证的专利组合。Intel尚未宣布代工业务的主要客户,而且SA最近报告称Intel的某个大客户已经跳船去了别家。

台积电、三星及Intel 10nm对比

via:semiwiki

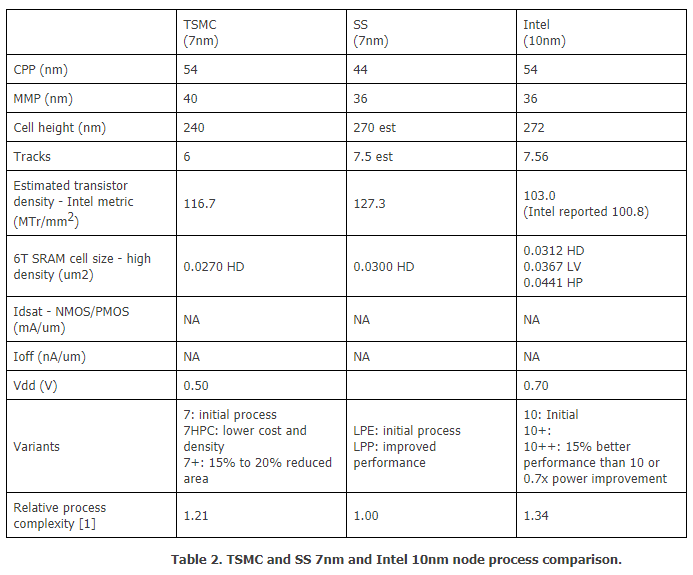

台积电、三星及Intel 7/10nm对比

via:semiwiki

Intel年初称首款10nm产品将瞄准数据中心。当时有点令人困惑,因为Intel传统的数据中心产品已经延后;然而Intel收购了Altera,所以似乎会是FPGA。大规模FPGA由于重复单元很多,所以可以在占据先进制程优势的同时,通过屏蔽和特挑依然能达到合理的良率。Intel下代FPGA将基于10nm制程,代号”Falcon Mesa”。

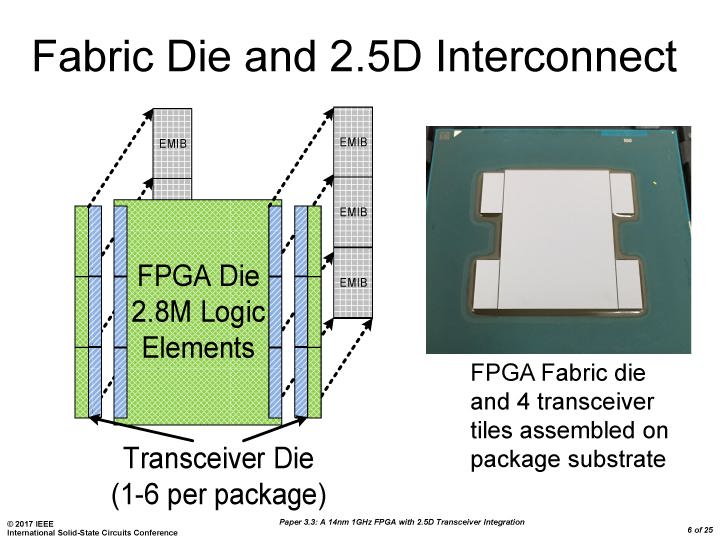

Falcon Mesa包含多种新技术,最引人注目的要算第二代Embedded Multi-Die Interconnect Bridge (EMIB) 封装。EMIB用额外的硅基板,为不同的晶片提供连接,连接速度比标准封装手段快许多;而成本比interposer要低很多。可以在封装里放进单个FPGA,然后在周围放上内存或者其他IP模块(可能采用不同制程),但都通过高带宽EMIB通信。Falcon Mesa也将支持下代HBM。

新一代FPGA通过EMIB连接的IP模块里,Intel列出的有112Gbps串行通信连接,以及PCIe 4.0 x16连接,支持每条16GT/s的传输速率。

关于10nm消费级产品则没有进一步消息。

via:https://www.anandtech.com/show/11850/intel-displays-10nm-wafer-commits-to-10nm-falcon-mesa-fpgas

原作者:Ian Cutress

MOEPC.NET编译,有删减,转载请保留出处。

比友商领先那么多就改个名字呗,8nm 9nm随便叫啊,智障么

@ssnitrousoxide:都是某家带的好头

amd的祖传ppt被intel偷走了?

看完这篇报道,我得出三点结论:

1. Intel PPT不可信。

2. 10nm工艺 Intel > TSMC > SS

3. 7nm工艺 SS > TSMC , 两者都比Intel 10nm工艺好。

@ayu:所以我都用的是”声称”….毕竟自家工艺肯定要吹

这三家10nm并不是同代…另外两家7nm才算是同代

和14nm一样,名字而已,GF14用的还是20nm后端

感觉这样intel核显上vega也有希望了。

@appleache:Intel上Vega是用McM

@1311abcd11:所以说是更有可能点

@appleache:好吧,我在想你可能是在说10nm低功耗加成

不过看最后一张图,图形部分跟核心一样是10nm的,所以看来Intel在它的10nm CPU上应该还是要用自己的核显…

@1311abcd11:我说的是EMIB封装,比mcm更灵活些,效率也更高。普通cpu肯定是没指望上vega了,一般肯定是苹果定制之类。特别是现在高分辨率,vr开始普及。