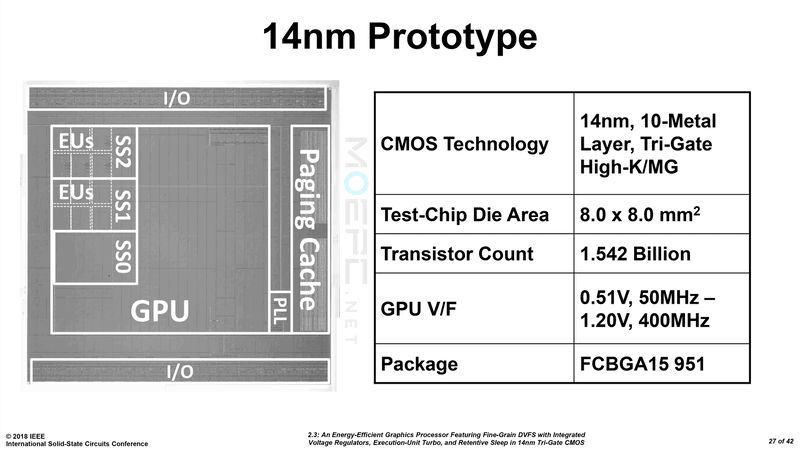

Intel 发表基于现有集显架构的独立GPU原型,14nm制程,着重省电【ISSCC 2018】

本文地址:http://www.moepc.net/?post=4381

Intel的GPU研发之一

Intel在ISSCC 2018上发表了独立GPU的原型。

Intel从AMD挖来RTG头头Raja Koduri,任其为核心与视觉计算集团首席架构师兼高级副总裁。有人认为这个戏剧性的转移标志着Intel将进入独立GPU市场。恰巧在这时,Intel在美国旧金山的ISSCC(IEEE国际固态电路会议)上发表了一款独立GPU的原型。

不过,这次的原型还没达到能上市的水平,仅仅是个用来技术验证的GPU罢了。它基于现有Intel集显架构,搭配IVR(Integrated Voltage Regulator)来验证功耗和性能控制技术。

过去,Intel也有过类似的低功耗验证GPU原型:2014年在ISSCC上发布的22nm 原型芯片(5.7 A Graphics Execution Core in 22nm CMOS Featuring Adaptive Clocking, Selective Boosting and State-Retentive Sleep」S. B. Nasir, et al., ISSCC 2014)。尽管如此,这款原型GPU具有完整的功能,做成产品也不是不可能的。

本文地址:http://www.moepc.net/?post=4381

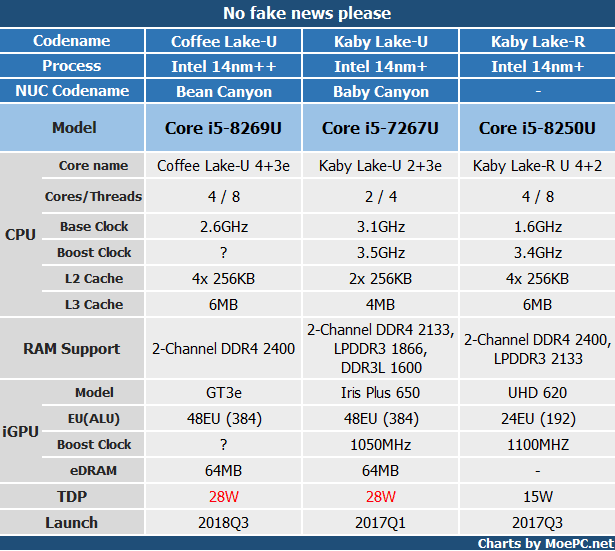

这块原型的架构为最新的Intel Gen.9,原原本本的Intel集显。不过采用的是Gen.9 LP,也就是Atom所用的低功耗集显,与桌面版的标准单元库不同。

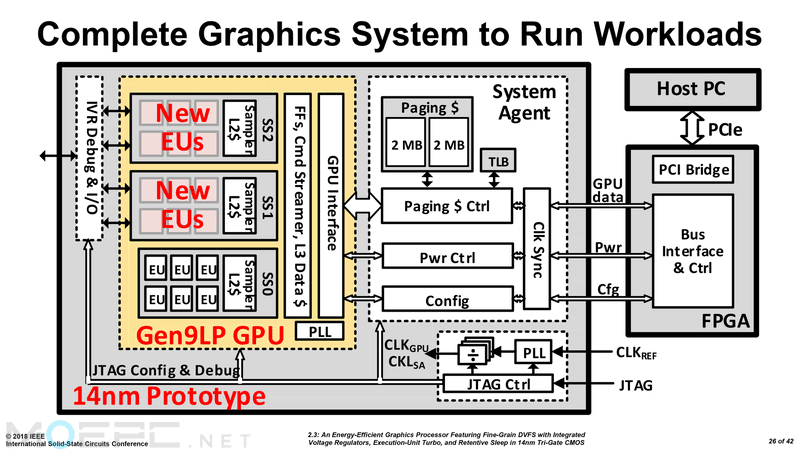

制程是Intel 14nm,10金属层(布线)。芯片面积为64mm2(8×8),15亿晶体管。工作频率和电压范围从50 MHz / 0.51 V到400 MHz / 1.2 V。晶体管这么多的原因是配备了大量的SRAM。

Intel推出基于现有集显架构的新设计

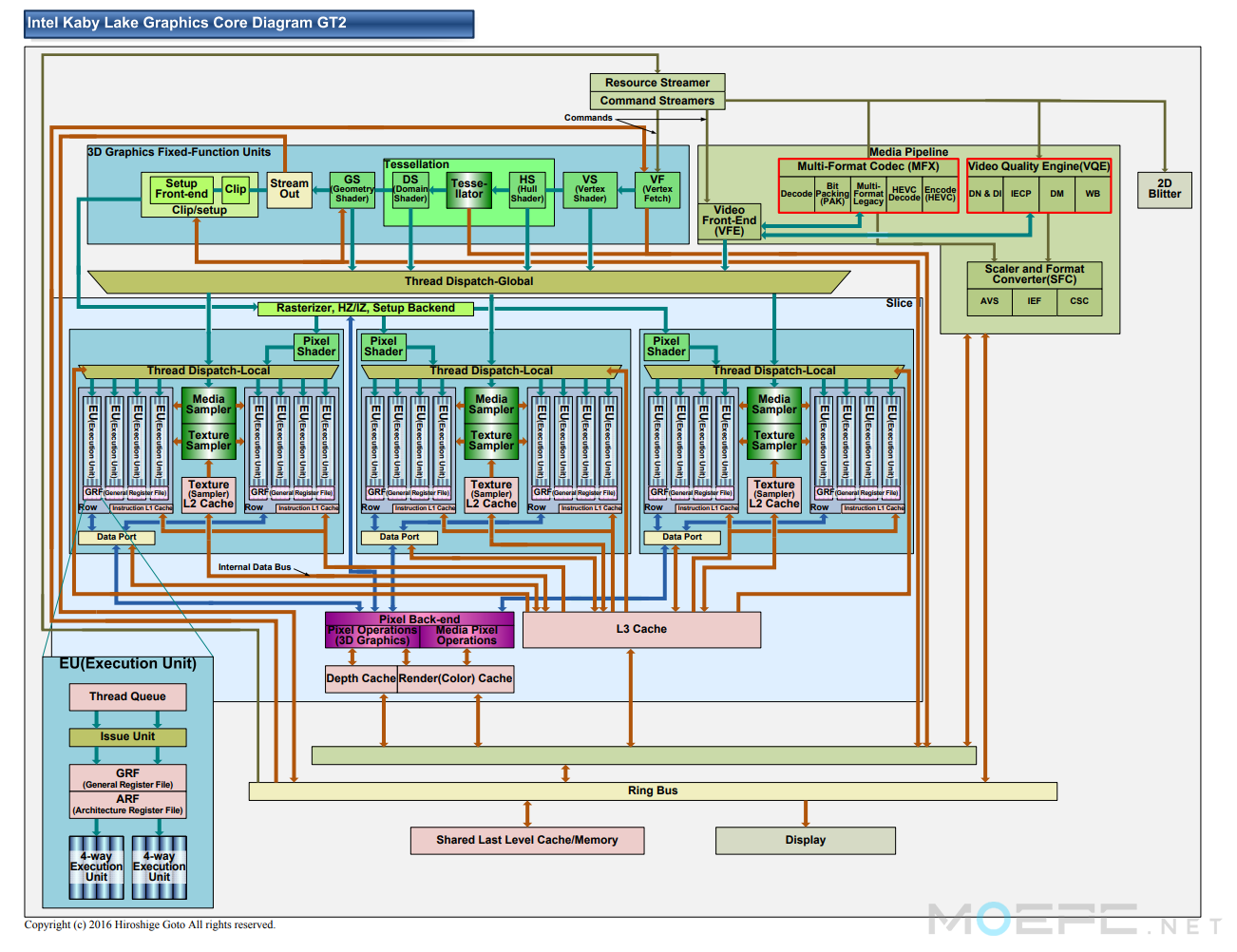

Intel的GPU核心由称为“EU(执行单元)”的向量核心组成。一个EU有2个4-way 向量单元。FP32单元为4-way、128-bit。EU由2个向量单元、7线程通用寄存器(GRF)、取指以及分支单元组成。

原型GPU中每个SS(Sub-Slice)里放了6个EU。除了EU之外,还有取样器(纹理单元),L1 / L2缓存,线程调度器,数据端口等。

原型GPU里由3个SS构成1个Slice,Slice拥有GPU的完整功能,包含显示固定功能管线、Command streamer和L3缓存等。图中可以看到编号SS0到SS2的3个EU,不过其中只有两个 – SS1和SS2是新的设计。

Intel Gen.9 GPU架构

也就是说这颗GPU共有1个Slice,3个SS,共计18个EU。向量单元中有144个 FP32 ALU。现在低端桌面CPU所用的GT1为96个,GT3e 384个,曾经的GT4e则达到576个。

144个低频【400MHz】Gen.9 LP EU,性能也就比较低端。而且通常集显会集成视频之类的多媒体解码/编码单元,这次却没提到。

在ISSCC上发表的这颗GPU不仅包括GPU核心,还搭载了包含控制和I/O的System Agent(SA)。内存接口在主机那边,出于这个原因,System Agent也配有4MB的大容量页面缓存。到主机是通过FPGA桥接的。光看这么个配置就知道它只是个验证用的原型了。

利用IVR进行细微的电压/频率控制

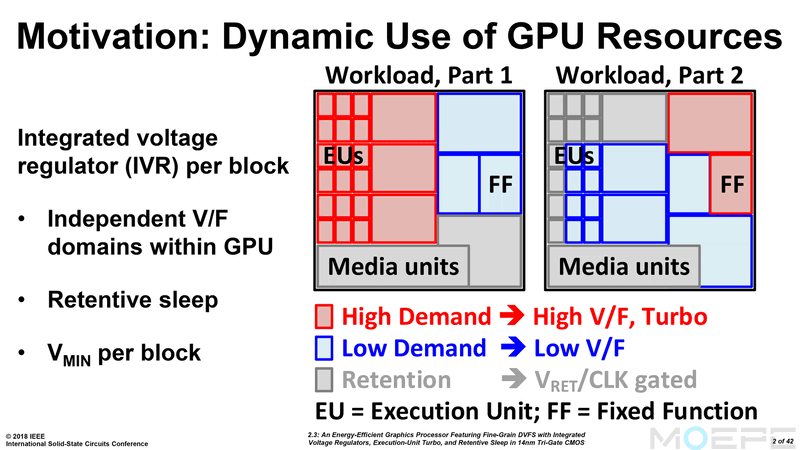

Intel这次的验证芯片主要特点是使用IVR进行细粒度的V / F(电压/频率)控制和功率门控。传统上,GPU的V/F控制和省电功能都要比CPU弱。因为普遍认为,传统的图形负载不是短时间的高负载就是非常轻度的负载,GPU厂商也就没在功耗控制投入太多。

然而,Intel验证称,通过在GPU内核中引入细粒度功率控制,可以在不同条件下改善能效。利用Intel CPU上优秀的功耗控制技术,改进后整合进GPU核心。如果在GPU上以粒细度运行各种任务,这种功耗控制应该会更有效。

其基本思想是,把GPU分为为一块块的小块,来以细粒度控制频率和电压,使得必要的模块以最佳的频率和功耗运行。与此同时,片上集成的IVR实现了高速电压切换。将空闲模块的电压降低至保持电压(Vret, 勉强足够保存SRAM数据的临界点 ),降低漏电电流。功耗门限(PG)则是通过可靠性更高的唤醒机制 – GPU内部各处的PG Driver来控制。

本文地址:http://www.moepc.net/?post=4381

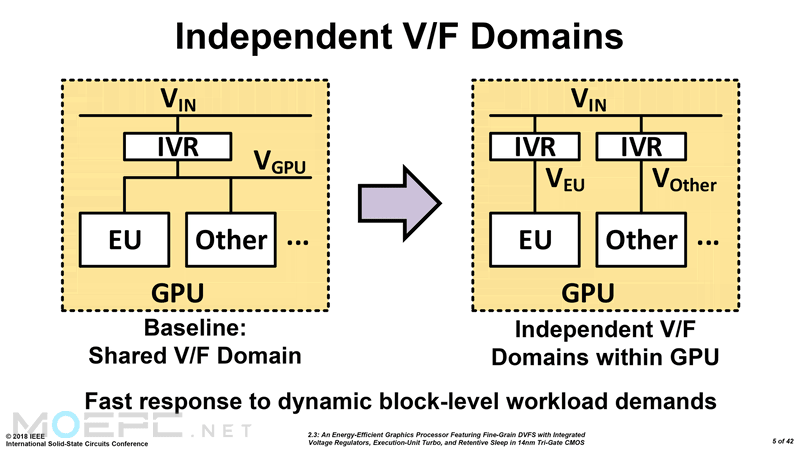

IVR的引入使得对每个单元的电压控制成为可能

传统的Intel集显设计是:整个GPU由单个电压(Vgpu)的IVR供电。相比之下新设计中,GPU中计算单元EU以及其他单元由各自独立的电压和IVR供电。

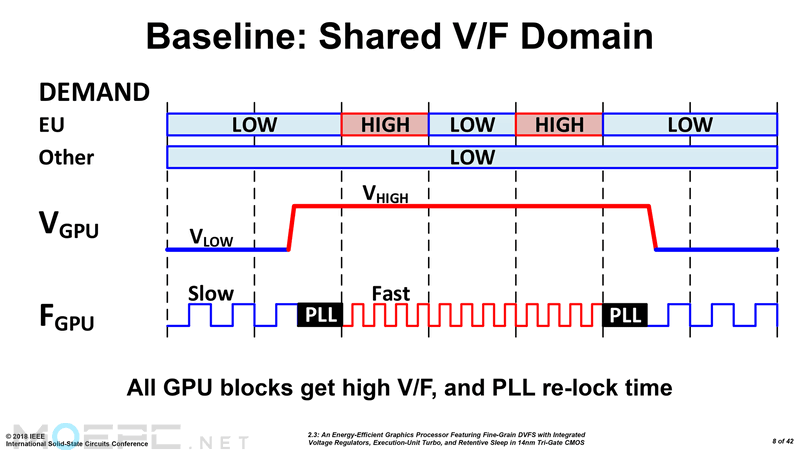

以前的架构里,当遇到计算密集型任务时,EU的负载会增加,从而导致整个GPU电压升高,同时时钟用PLL re-lock切换至高频率。当然除EU以外的其他单元也被提到和EU同样的电压、频率,导致GPU整体功耗上升。

老架构的V/F控制

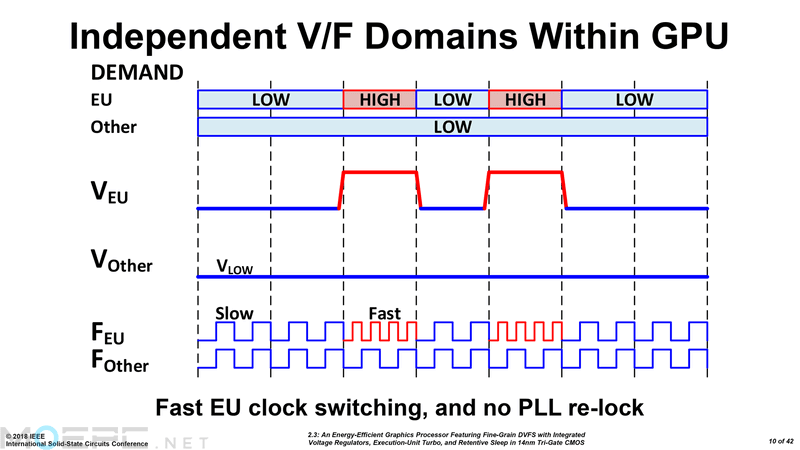

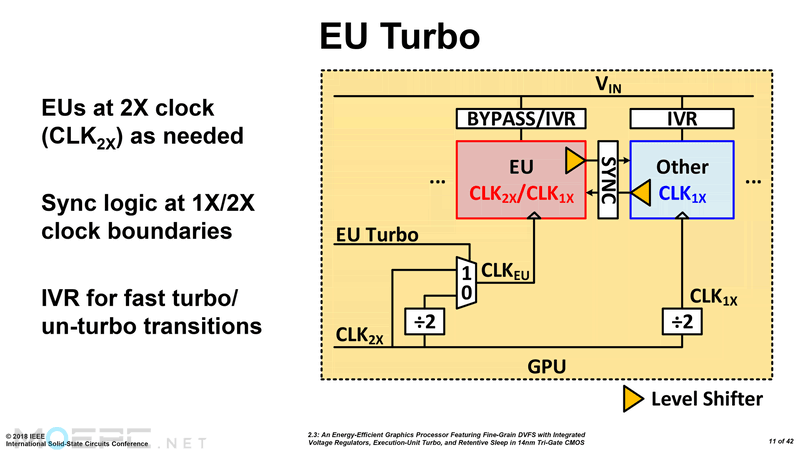

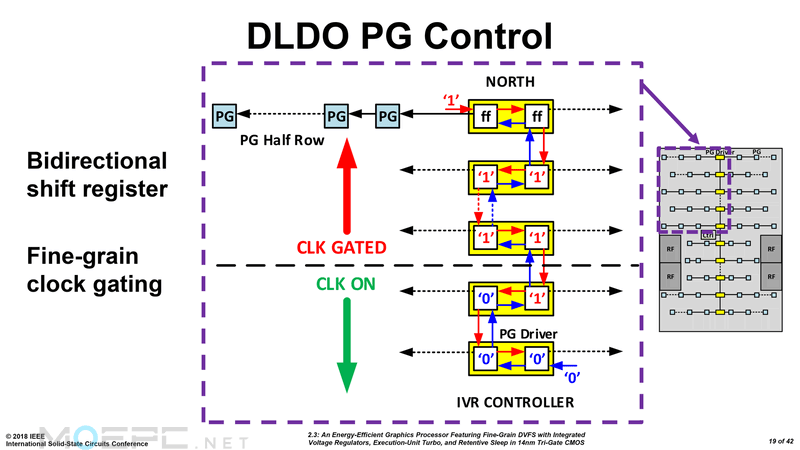

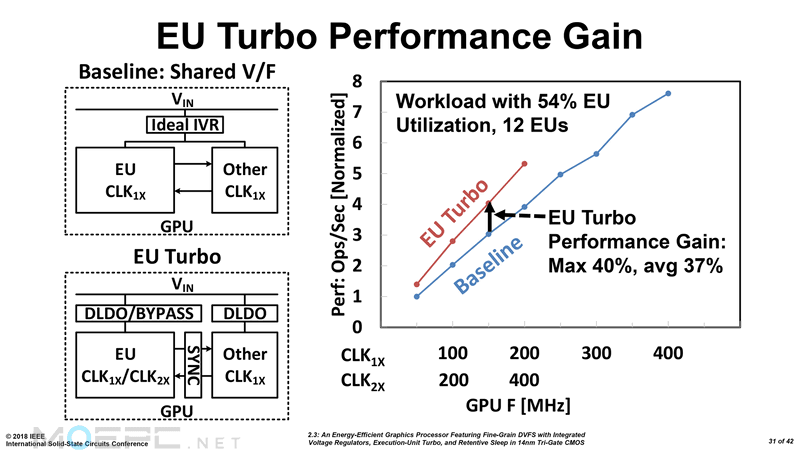

如果EU和其他单元的频率和电压控制分开,就能够更加灵活。此时只有EU的电压会升高,频率提升至正常的两倍。通过单独配置高响应度的IVR,可以在短时间内提高电压。

新架构的V/F控制

本文地址:http://www.moepc.net/?post=4381

另外把频率切换到原来的2倍就不需要PLL re-lock了。Intel称之为“EU Turbo” – 加速时为默认的两倍频率,一般情况下则为加速的一半频率。可以根据负载快速改变电压/频率。

EU的CLK 2x

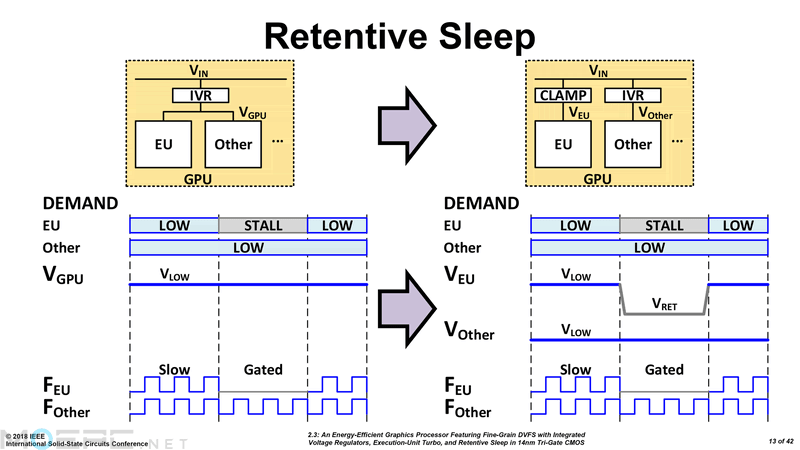

相反,当EU短时间闲置时,会将EU的电压降至保持电压Vret,进入切断时钟的睡眠状态。以前的话是没法在时钟门限(Clock Gate)的同时降电压的,这次改成了独立IVR就可以尽可能的降低电压。

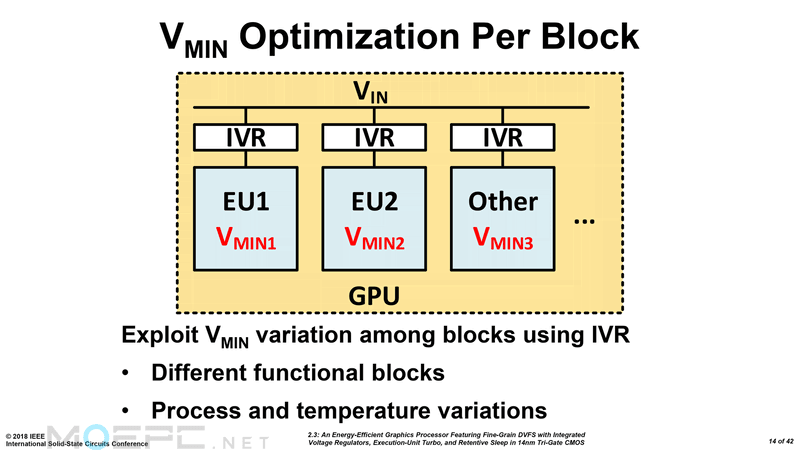

此外,通过为每个EU单独设置IVR,还可以调整运行最低电压Vmin的稳定程度。不仅是制程自身的稳定性,还有温度带来的波动,有了IVR就可以动态调整每个单元的Vmin,设置为各自的最低电压。

以块为单位调整Vmin

GPU内集成两种IVR

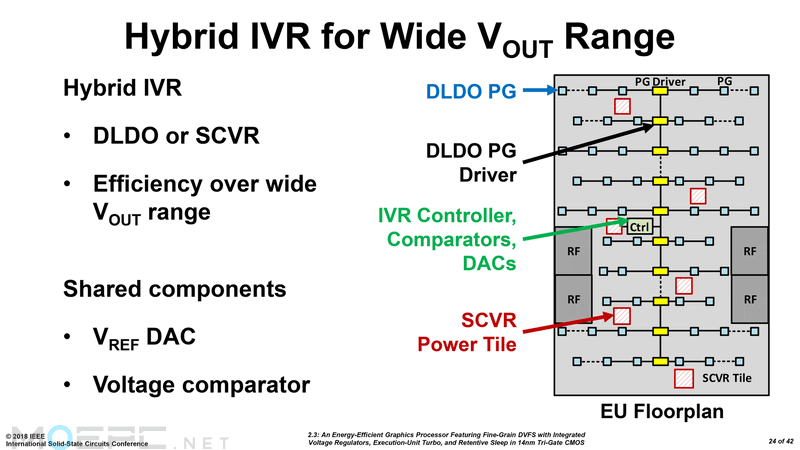

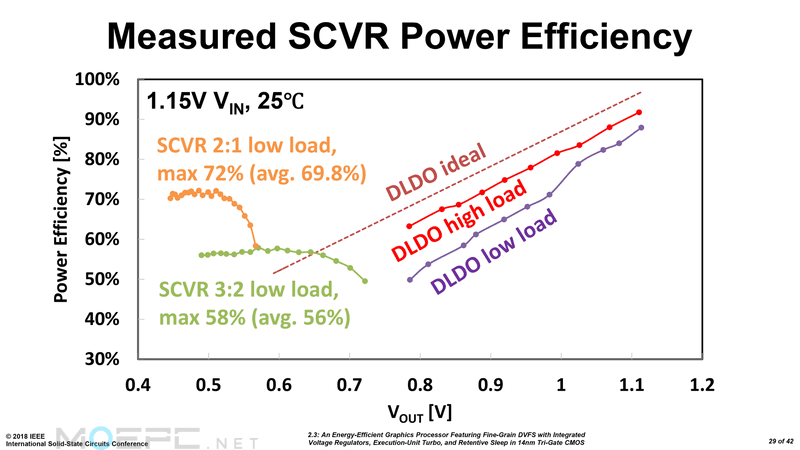

这次原型芯片所集成IVR的设计特点:混合了两种不同类型的VR。除了以前的“Switched Capacitor VR(SCVR)”以外,还配合了“Digitally Controlled Low Dropout(DLDO)”。两种类型的IVR在更大的电压范围内实现高电压转换效率。

通常运行时,当输入和输出之间的电位差很小时,使用DLDO。比如1.15V的输入电压(Vin),输出电压(Vout)约为0.785V至1.11V。细粒度控制也基于DLDO。当输出电压低至0.3V至0.7V时,使用内置MIM电容器的SCVR。此时输出相对于输入的电位变为3:2,2:1,3:1的比率。

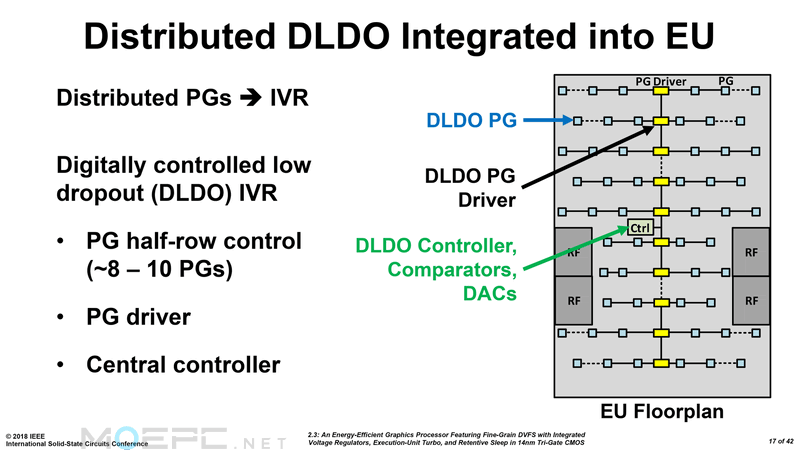

在EU内部,SCVR被配置在6个tile中。IVR控制器则位于EU中央,DLDO PG Driver的排列类似于骨髓,延伸出EU各处的DLDO PG。据说DLDO PG有1400个以上。

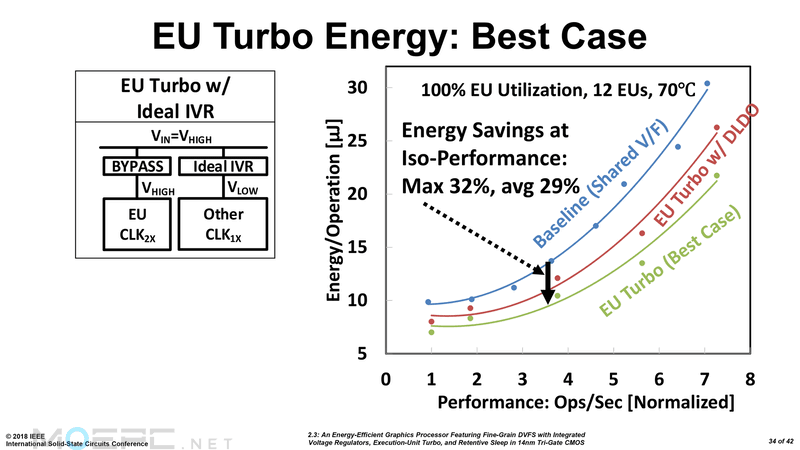

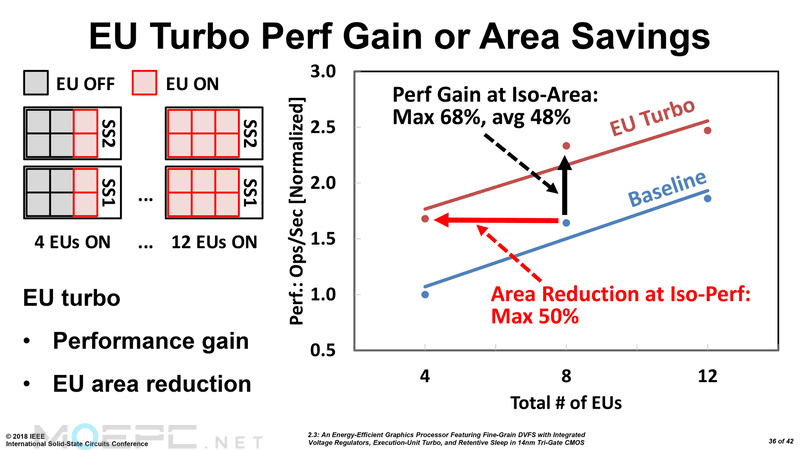

对于新设计的12个EU而言,在EU负载54%的情况下,EU Turbo的性能将提升最多40%,平均37%。当EU使用率达到100%时,EU Turbo的功耗比基准降低最多32%, 平均29%。而且通过EU Turbo提升EU的运行频率,再功耗门限部分EU,可以同时实现提性能和降功耗。

虽然这次的原型GPU还没达到成品等级,不过可以看到省电控制设计的大体方向。Intel自从Haswell引入IVR,现在不光CPU,GPU核心也要引进IVR。省电控制正是Intel不为人所知的强项。

【看来和此前预测的一样,Intel对于GPU的研究在Raja跳槽前就进行了很久。

进度可能会比预想的要快。】

本文地址:http://www.moepc.net/?post=4381

via:pc.watch.impress.co.

jp

原文作者:後藤 弘茂 (Hiroshige Goto)

MOEPC.NET编译,有节选和修改,转载请保留出处。

不看好英特尔做独立显卡。

为什么评论歪楼了…

@剧毒术士马文:从黑阿三开始吧

然后我说了句阿三带了新的设计组和总工才走的

之后我就看不懂了。。。。。。。。。

@剧毒术士马文:台达电源 稳定省电 无悔的选择!

@轮子妈:谁知道现在科血上网怎么弄,听说ss不行了。我想在生产机器上开ss有些犹豫。谁给个建议?

@amdfan:V2Ray VMess协议

@amdfan:使用非常见机房,非常见端口吧。

个人感觉,AMD的硬件架构现在暂时不是主要瓶颈,关键是驱动团队。

题外话,自从Intel驱动团队把Gen5以前的驱动转为维护以后,连续给Gen6+出了两三个版本的功能/优化驱动,但是完全没有人关心。A卡群众以前出一个驱动看着Changelog写的性能提升就跑分的劲头现在也没啥了。

[划掉]要是在前几年催化剂时代VEGA出来到现在性能已经在changelog里提升20%了[/划掉]

@hyno111:深红驱动,还好啊= =

我个人感觉A驱动比N驱动好用很多

@桜道月:个人认为Raja对RTG部门,最大的贡献莫过于深红驱动了。

@ayu:我觉得Vega 是一款成功的产品

本来是懒得打那么多字的,但看到评论区居然还有人对AMD卡盲目乐观,甚至对Raja冷嘲热讽的,有感而发。

我都不知道这些人到底是黑还是粉。

再说生产

面对矿潮,NV显卡是涨价,AMD显卡是根本买不到。

这个是产能的巨大差距,GF和TSMC根本就是小作坊和自动化工厂的区别。

工业生产中,一般产量越高,单位成本就会越低,GF和TSMC产量差别巨大,P10面积还比GP106大一圈,居然还有人认为GF的工艺便宜,老黄成本高?GP106即使学470D切掉22%的规格,价格砍到1/2,毛利率仍然比470D这种卖血的玩意儿不知道高到哪里去了。

成本高了影响议价能力,AMD想盈利,经销商自然就没啥油水了,所以现在人家都不爱卖A卡。

@xing0999:7nm节点上按摩店会同时使用TSMC和GF的7nm, 应该可以安心的

AMD成本要谈的得说Vega吧,根本没多少办法压价格,已经见过的V56 2800+可能是最低的价格了

貌似1080要真正压成本价也就是1500的价格?

@xing0999:lisa su自己都在电话会议里说了,产能不足是因为gddr ram和hbm供应不上,silicon方面没有问题。这些都被您有意忽略了?还在这里喷GF的产能问题?

当然,AMD能不能像NV一样拿到那么多ram supply就不好说了。但那又是一回事了

到2018年,NVIDIA市值已经是AMD的接近15倍,离INTEL都不远了。我不知道AMD如何才能面对一个体量是自己15倍的对手,更何况AMD研发资金ZEN团队还要分掉一大部分。

事实上从核心数量上来看AMD都已经输了

在16年,老黄GP100 102 104 106 107 108整整6个核心,完整覆盖通用计算-高性能-主流-入门-轻薄的所有细分市场。

AMD 16年有啥?P10和P11,P10刚刚战平106,功耗和成本都被吊打。P11完整核心都不能控制在75W,砍一刀之后性能比1050ti低,功耗和成本还高。

这篇科技文章技术含量逆天了,看了下作者“后藤弘茂”,我也就不奇怪了。

事实上AMD自从hawaii核心之后便已经后继乏力了,还是Raja带领团队打通了HBM这条路强行又给ATI续了一波

Raja在位这段时间,没有新战略新研发,只能苦撑(可以百度阿三在位期间AMD市值以及RTG盈利状况),他能利用现有资源把GCN进化到这种程度已经实属不易,毕竟业界所有图形人才/研发资金基本上都集中在友商那边,巧妇也难为无米之炊,理想在现实面前也得低头。

Raja在的时候,没有新架构,但至少还有新核心,Raja一走,新核心都费劲。我很想知道AMD在Navi以后还有没有新战略,大概在此之前就已经转型去专门做半定制了吧(笑)

@xing0999:NV ≠ 友商

替代RAJA的大胃王问题应该不大吧…

http://www.moepc.net/?post=4201

@xing0999:拉贾从来都没有所谓的打通HBM线,也不存在给ati续命这一说。事实上对于2012年以后专业卡薄弱的amd来说,HBM理论上的高带宽没有任何性能增益。Fiji使用HBM的原因只有降低整卡功耗分给频率达到极限的核心,还有就是尽量差异化竞争。也不要把拉贾当值期间的AMD市值之类的无关变量拉进来,事实是Polaris、Fiji、Vega从来就不是AMD的救命稻草,而是ZEN系列的上市。至于你所说的新核心,好吧,至今没有一个业内人士敢于做出这些GPU“创新”“前卫”“建设性”的评价。当然你说得对“巧妇难为无米之炊”,不过拉贾到底是一个怎样的人,不要做诛心之论,而是要看实际结果。

PS:说得难听一点,作为消费者,不值得也不配去关心厂商的战略,这种行为不过是在脑内翻腾金融巨浪的自我满足罢了。不过董事会成员除外

@在amd看大门:哈哈,最后一段说得好

AMD在ISSCC2018上介绍了zen架构互联的许多细节,可以考虑在网站发一篇

阿三会怎么带领INTEL呢?

@wangbaisen1990:他能不把Intel折腾塌就是好事。

@永之:噗不可能的啦

你这黑的过分了

不正经的说一句,很期待那个印度人把Intel折腾死(个人认为因为这家伙主导的RTG是这几年amd搞不出好GPU架构的主要原因之一)

正经的说一句,就算放弃larrabee这么多年后Intel依然没有放弃在当年在GPU领域的野望啊。。。

@zdawny:肯定不会放弃的,毕竟phi计算卡都出了这么多代

@zdawny:调侃阿三算风趣,真黑阿三算傻x

Raja是AMD 14年专门从苹果手里迎回的GPU,是AMD阵营里面硕果仅存的ATI高级工程师,我想目前在整个RTG没谁比Raja更懂GPU。他的离开,标志着ATI从此已经成为历史,农企也不可能再从业界里挖来更好的人选了。

@xing0999:带出了新的设计组 好像有新的高级工程师了,不能简单的这么说了,就和ZEN那个一样

@wangbaisen1990:Raja和团队的关系就是1%天才和99%汗水的关系。

@wangbaisen1990:再说,Jim Keller如果真的想养老,AMD大可以在文职部门随便找个闲职,给Jim高薪供起来,CPU设计上如果出了什么偏差,Jim还可以随时来给点人生经验。

但人家还是走了,为什么?待遇留不住人。

Jim回来完全是为了AMD情怀,情怀完了人家也要养家糊口。AMD就像国内部分研究机构一样,给情怀不给待遇,留的住人才怪。

@xing0999:额我的意思是RAJA和ZEN那个keller一样虽然都是走了, 但是都是带出来了新的设计组和总工程师

@xing0999:JIN KELLER想设计低功耗芯片吧。。问题是当时A根本没经费去弄啊。。。。

@xing0999:AMD vp level的待遇怎么留不住人了?您如果是业内人士有消息呢,就请分享一下,不然我只能认为您是拍着脑袋张口就来了

@xing0999:你在评论里留下太多出于情感的回复了,比如这条。不知道你是如何联想到“给情怀不给待遇”的奇谈怪论。想来一个生命几十年的美国IT公司原来是不给子系统总经理签职位协议的?至于Jim Keller,jesus,那么你可以解释一下之前他不断跳槽是为什么吗?不要把一个项目的成败归于一个人身上,在这之前AMD经历过比这惨烈得多的人事调动,结果并不可怕。而如果想用拉贾离开这个论点去证明“AMD药丸”,只能说这个出自于石村号的话术并不高明

@xing0999:问点问题

被挖回来的David Wang,技术水平够不够带领RTG?据说是R300-GCN都有参与开发

还有有不少传闻,说RAJA在A内部开小杜乱投资公司,比如投资阿三开的VR电影公司,NV当时都评论,说根本不可能赚到钱

@5256qpqp1:以RTG这个烂摊子,黄仁勋来都无解,AMD差的已经不仅仅是一两个工程师了。

Raja不管风评如何,才学是实打实的,少这样一个工程师对AMD没有好处。

@xing0999:实力是业界公认。。。但是素质就。。。就我听来的消息,RAJA滥用职权以致到RTG内部闹矛盾的程度了了,烂摊子这件事,RAJA至少有一半责任,当然另一半就是LISA SU砍经费了

@xing0999:事实上 AMD内部对阿三不满的很多 主要集中在中饱私囊 和阿三拉帮结伙