AMD Next Horizon活动汇总:发布首款7nm GPU Vega 20,揭晓更多Zen 2架构信息,64核“Rome”性能演示

【18/11/14 补充AMD对Zen 2 IPC的说明、“Rome” 64核频率及双精度性能、Shasta超算的规格等消息,可以在文章相应部分红色字体找到】

AMD就在刚刚举办了Next Horizon活动,这次活动是针对数据中心的,不是普通的消费级产品发布。在活动上AMD宣布与亚马逊AWS的合作,发布了首款搭载Vega 20的显卡:Radeon Instinct MI60,揭晓了更多关于Zen 2架构的消息,同时现场演示了MI60和64核 Zen2 EPYC “Rome”的性能。本文将直接涵盖所有活动的内容。文章内容并非活动发布的顺序,是我重新整理过的。

活动的主旋律是TSMC 7nm – N7 HPC制程下的产品。HoriZon的“Z”里有个”7″。

点击相关标题跳转到文章内容。

- 世界首颗7nm GPU – Vega 20,主打HPC,PCIe 4.0

- TSMC N7 HPC制程

- Zen 2架构:前端及浮点大幅加强,29% “IPC提升”?

- 基于Zen2架构的EPYC,代号“Rome”

- “Rome”原型单路主板 技嘉MZ32-AR0

- N7 HPC密度、Zen2芯片面积相关

- “Rome”性能演示

- HLRS的“Hawk”超算将采用“Rome” 64核处理器,曝光“Rome” 频率及性能信息,单路双精度 2.4 T

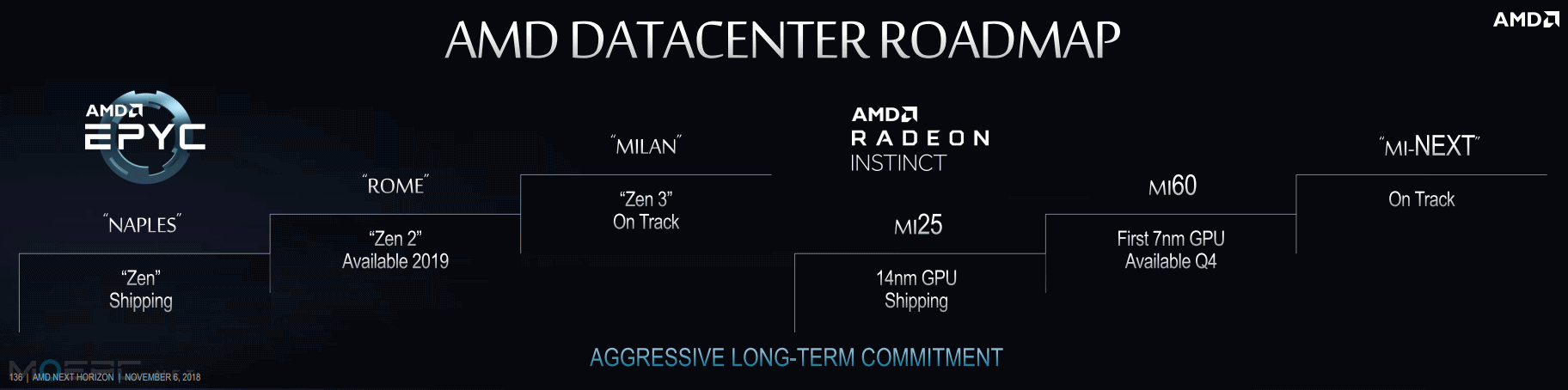

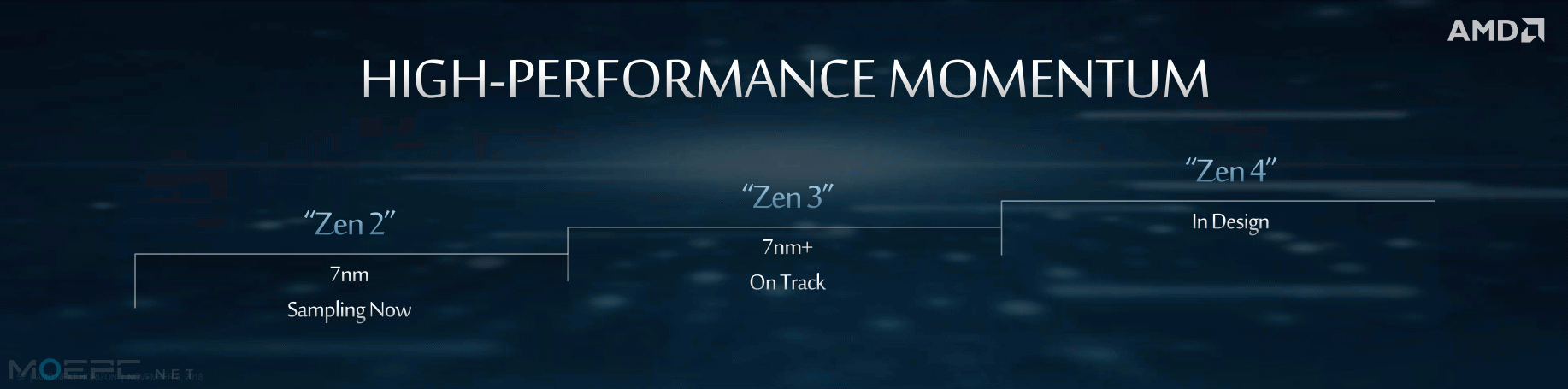

- EPYC路线图更新,Zen4研发中

- 亚马逊AWS部署EPYC主机

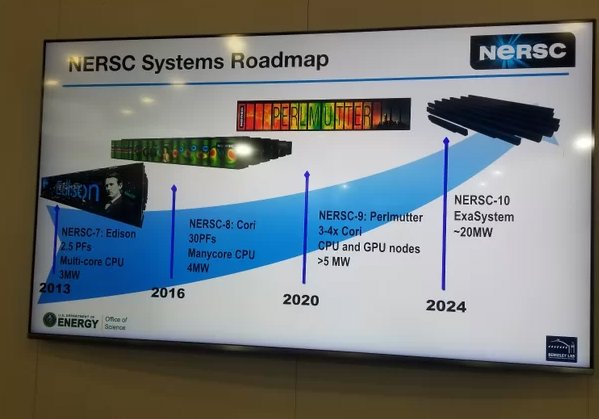

- AMD与CRAY合作打造超算 NERSC-9,“Shasta”将采用Zen3 “Milan” EPYC CPU

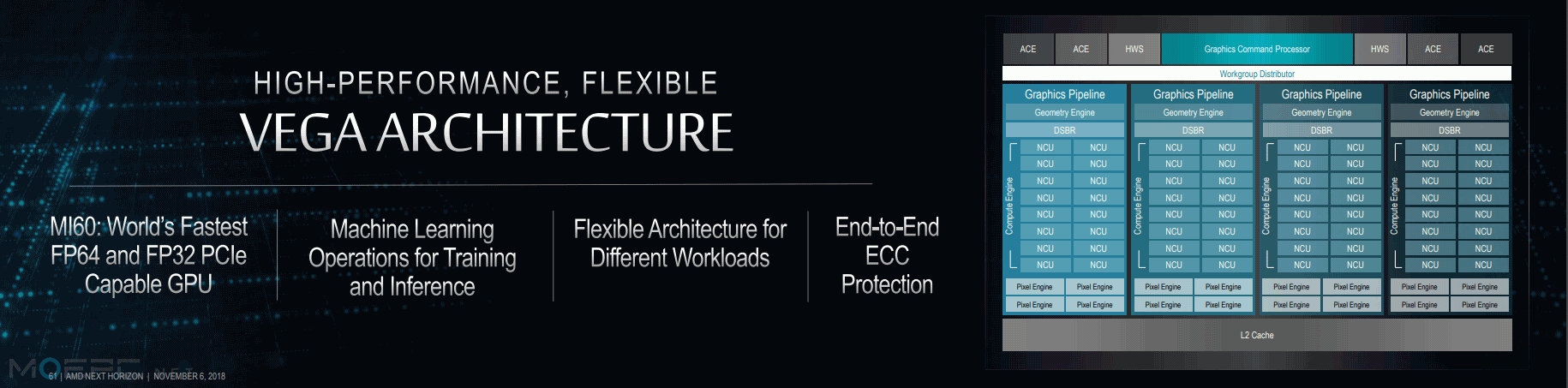

世界首颗7nm GPU – Vega 20,主打HPC,PCIe 4.0

作为今年最后的发布之一【后面估计就还剩个P30】,Vega 20的规格大概是最没有悬念的了。

64CU + 32GB HBM2,1/2 FP64,PCIe 4.0。和之前的消息一致。

【btw:虽然AMD发布上没有提到Vega20,但David Wang在台上的时候一不小心说漏嘴了hhhhh:

David Wang:”(ROCm 2.0)….It comes with Vega twen…MI60″】

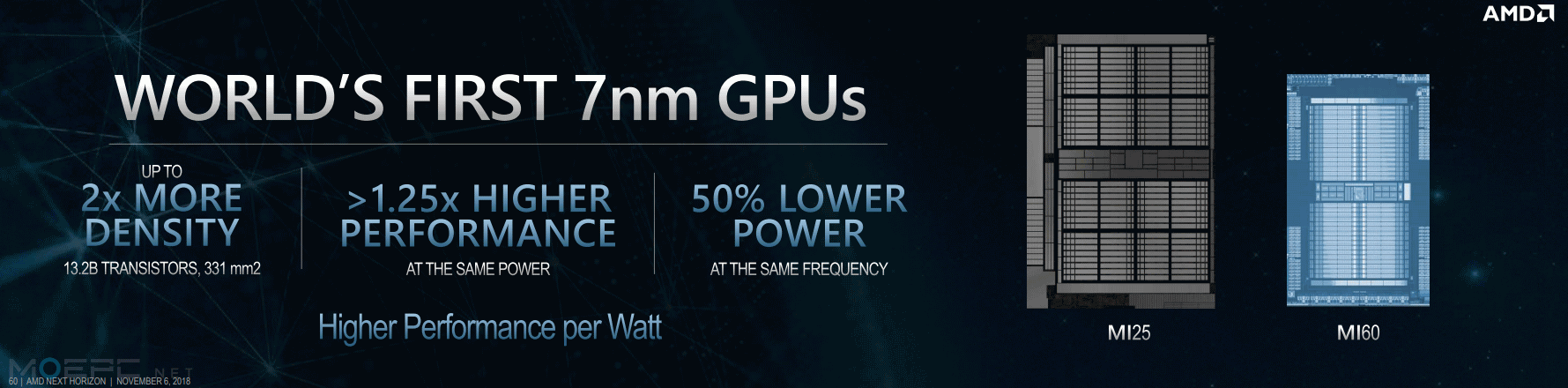

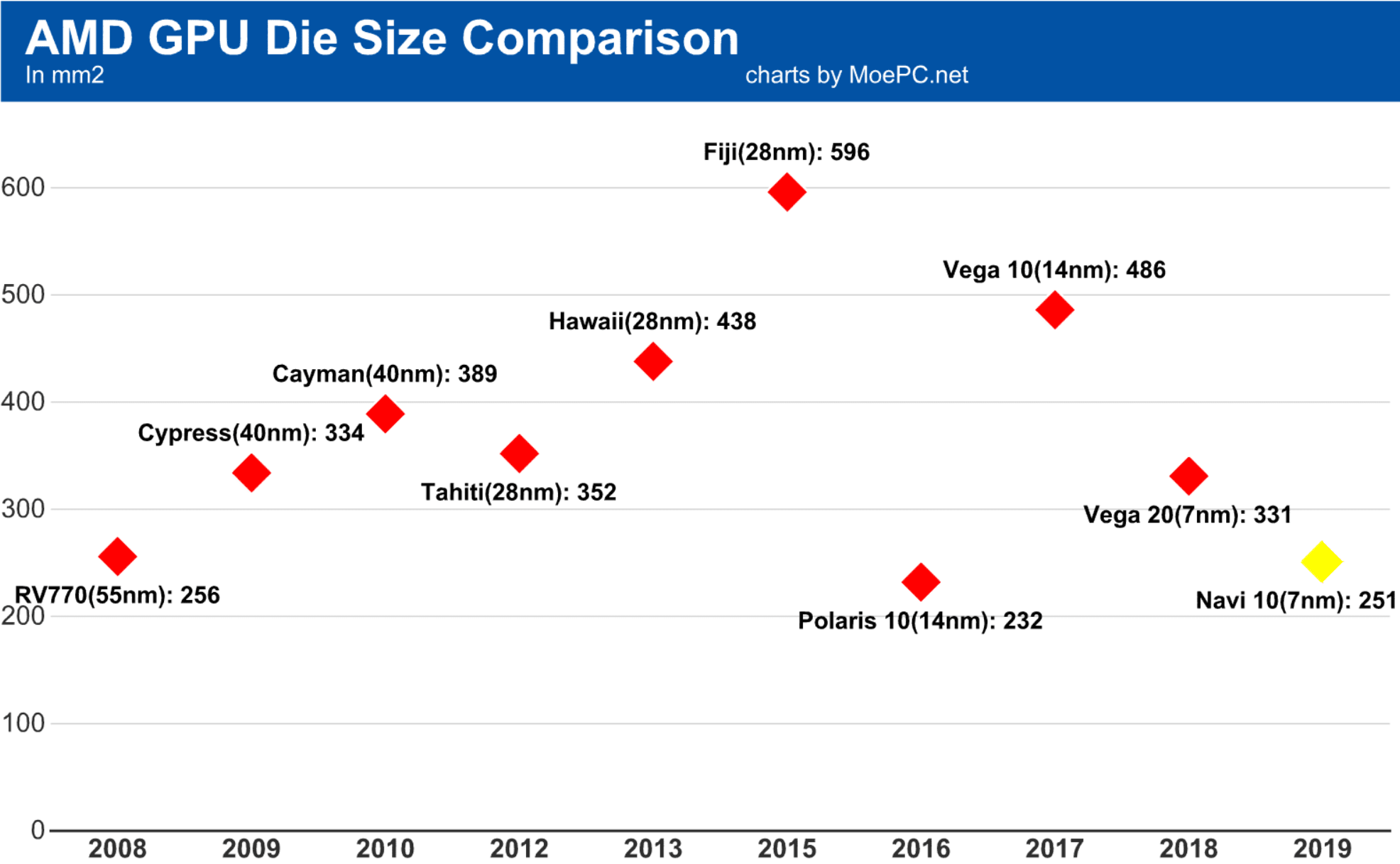

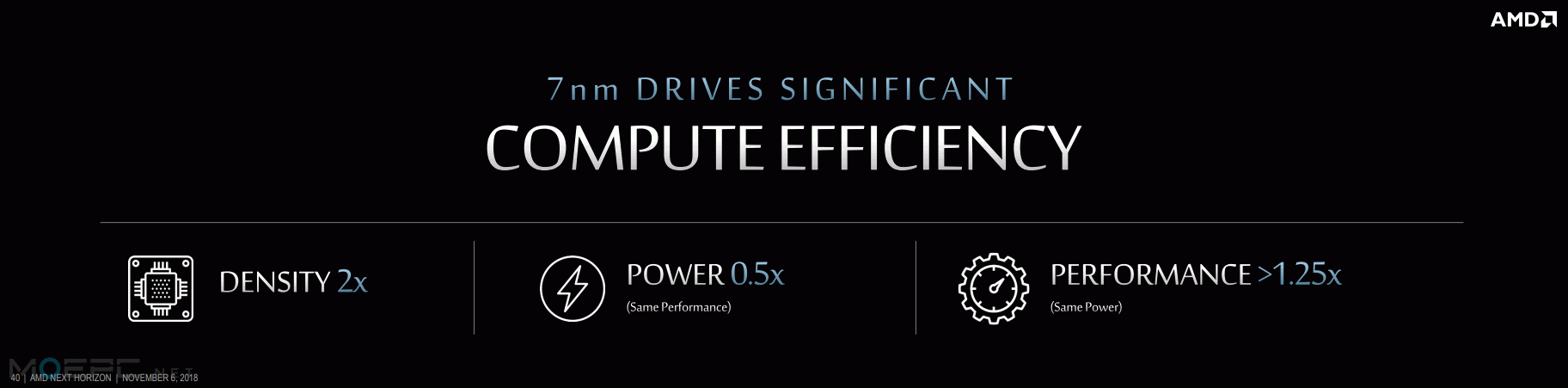

132亿晶体管,331mm2面积。N7 HPC带来了最多2倍的晶体管密度,同等功耗下1.25倍性能【其实就是频率】,同等频率下降低50%功耗。

简单算下就知道N7 HPC的密度比手机芯片用的N7 SoC的要低很多。

【官方都说了是最大2x密度提升。N7 SoC是3.3x,比如Kirin980的69亿晶体管,面积只有74mm2】

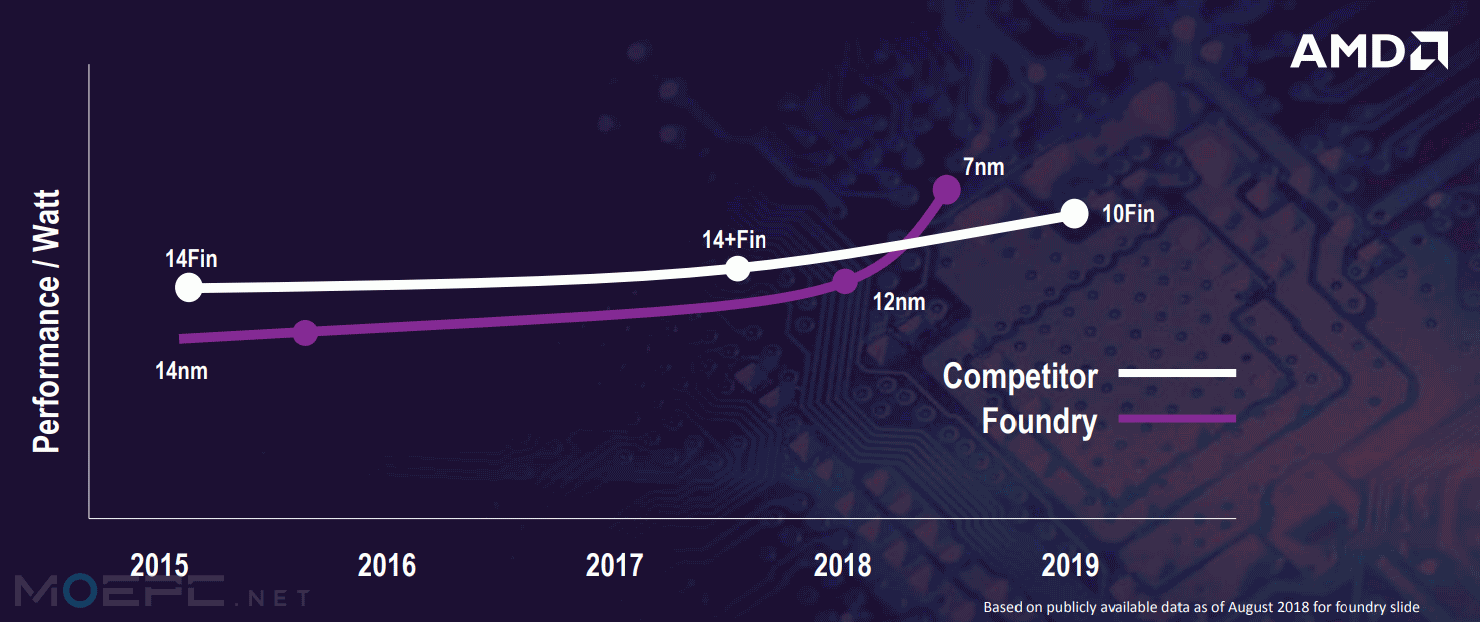

N7 HPC主要为高频率优化。在能效、密度上相比Intel 14nm有着明显优势。

Vega 20是AMD在N7 HPC上的第一款产品,可能也充当着试水的角色,不一定完全利用了N7 HPC的密度。

【更新:Vega20的某些部分晶体管密度更高,推测是为了缩短设计周期,同时又能够用到7nm的频率和功耗优势的考虑,所以并不能很好地反映N7 HPC的实际密度。而且有些IO电路在7nm下并没有减小多少面积。】

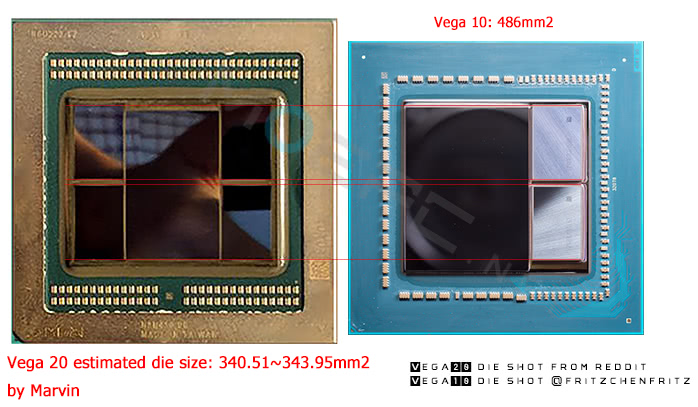

几个月前预测的是大概340mm2,差了9mm2。有误差是难免的。

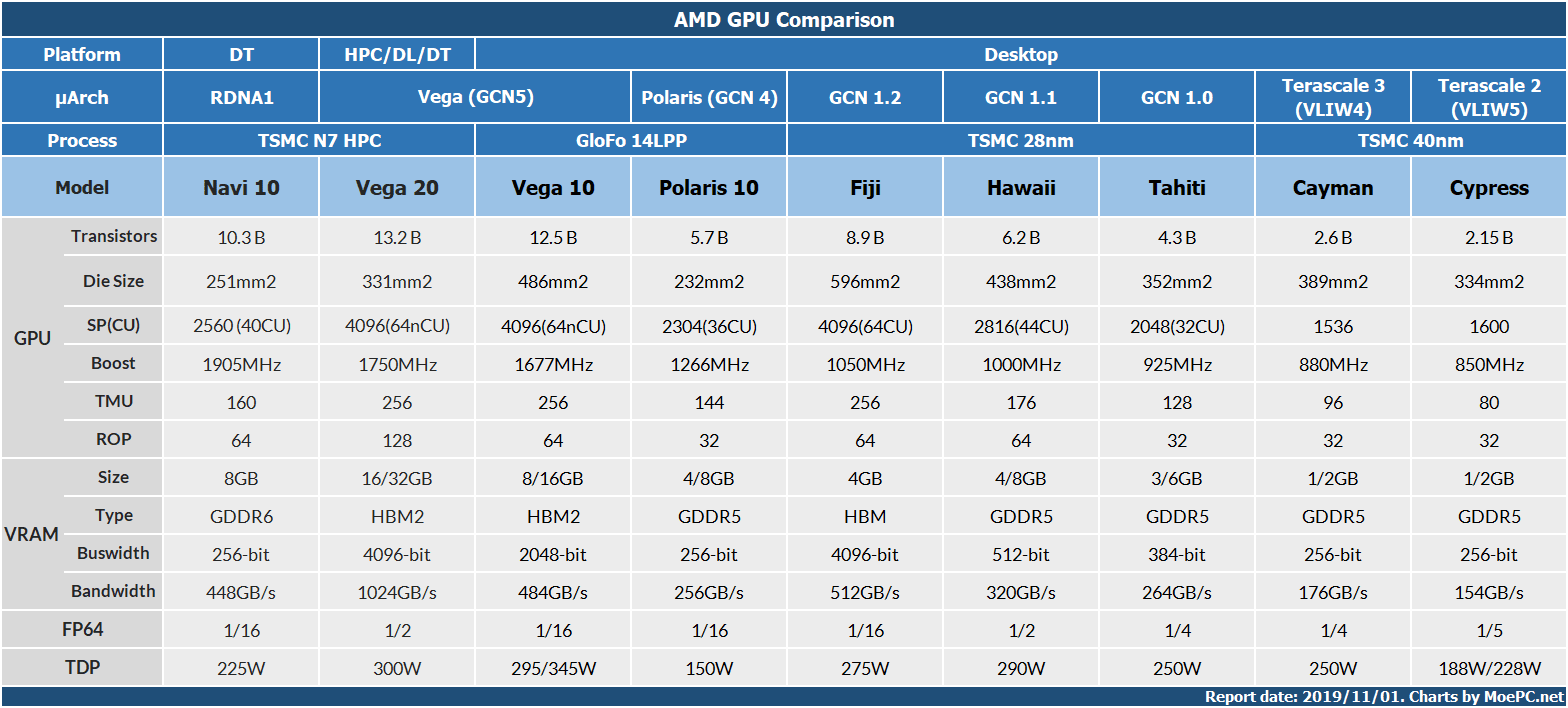

331mm2大概是Cypress【HD5870】和Tahiti【HD7970】的面积。

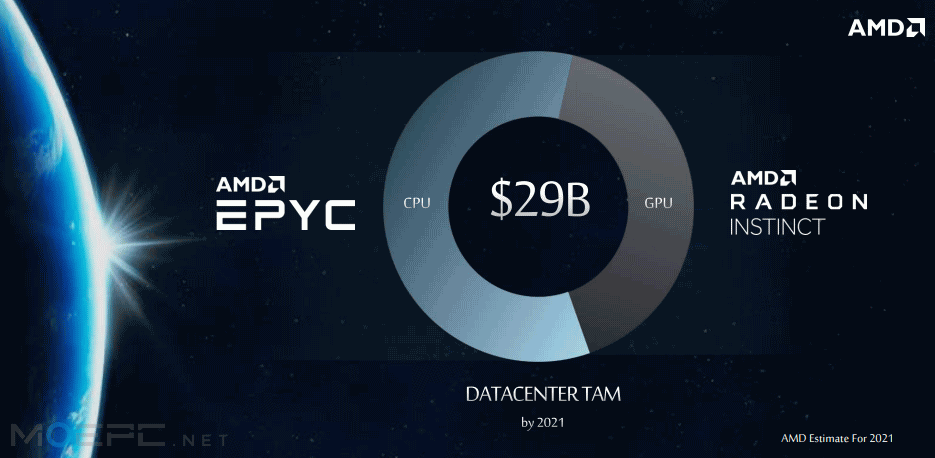

Vega 20主要瞄准数据中心市场,根据AMD预计该市场在2021年之前会达到120亿美元的TAM。

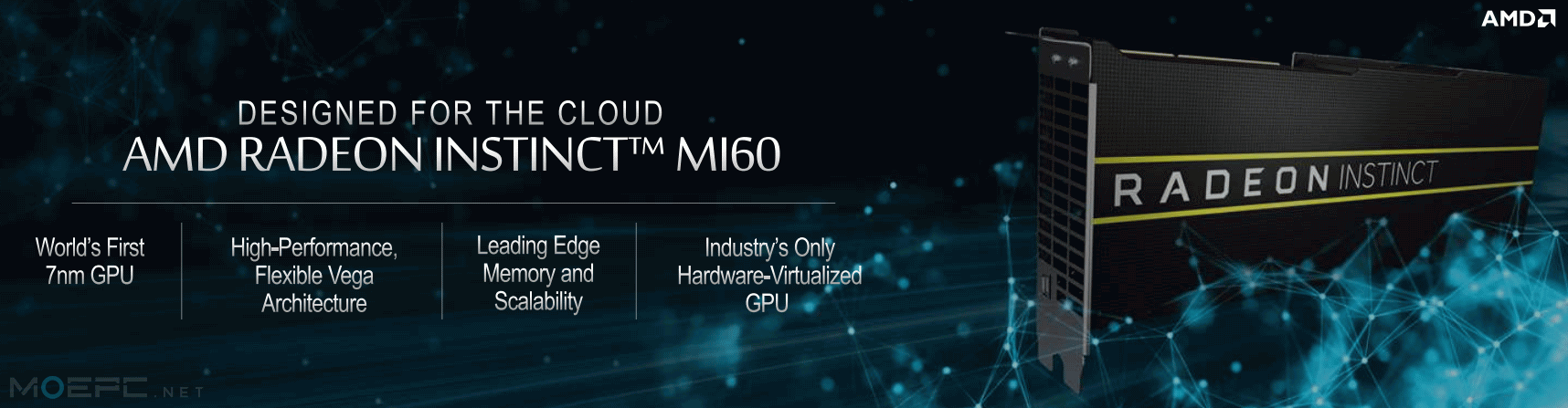

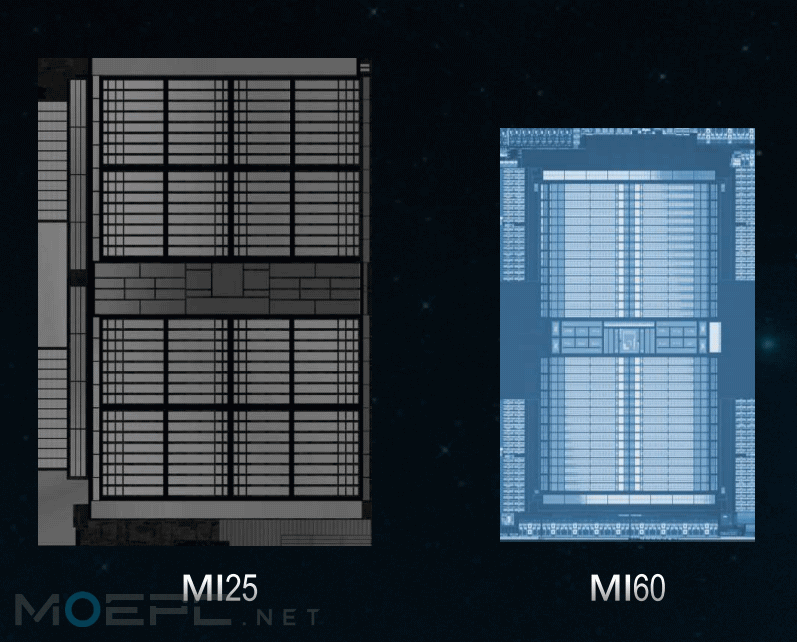

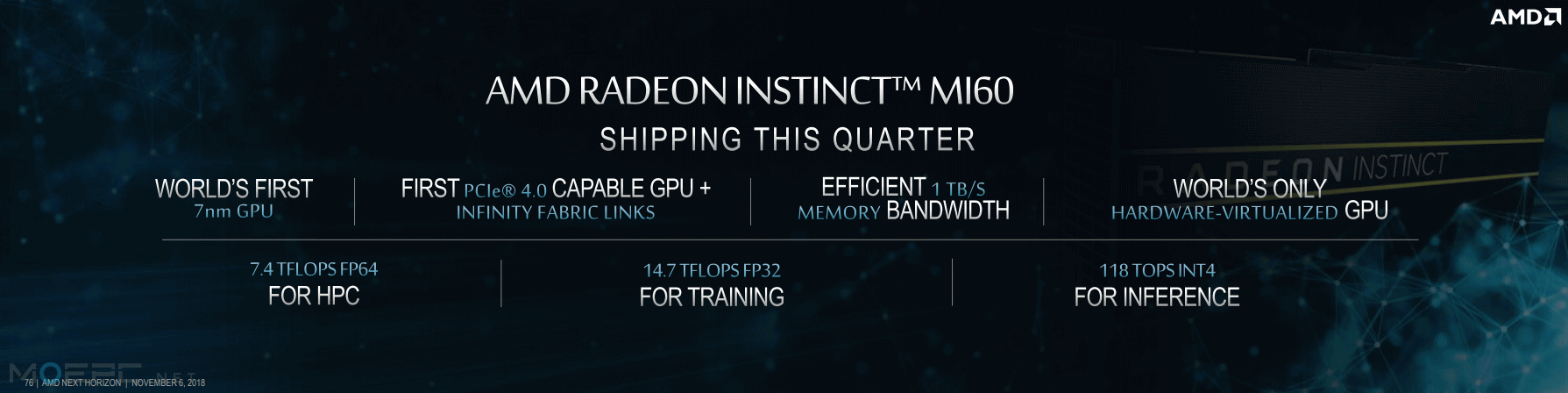

搭载Vega 20 GPU的首款产品为Radeon Instinct MI60,也就是会上发布的这款,4096SP,32GB HBM2。

Radeon Instinct MI60会是Vega 20的完整旗舰版本,AMD声称它是目前市面上最快的FP64/32 PCIe GPU。

MI60可以说是在MI25的基础上,向运算速度【INT8,机器学习】和运算精度【FP64,高性能计算】两头延伸。Vega20支持更多深度学习需要的指令集。

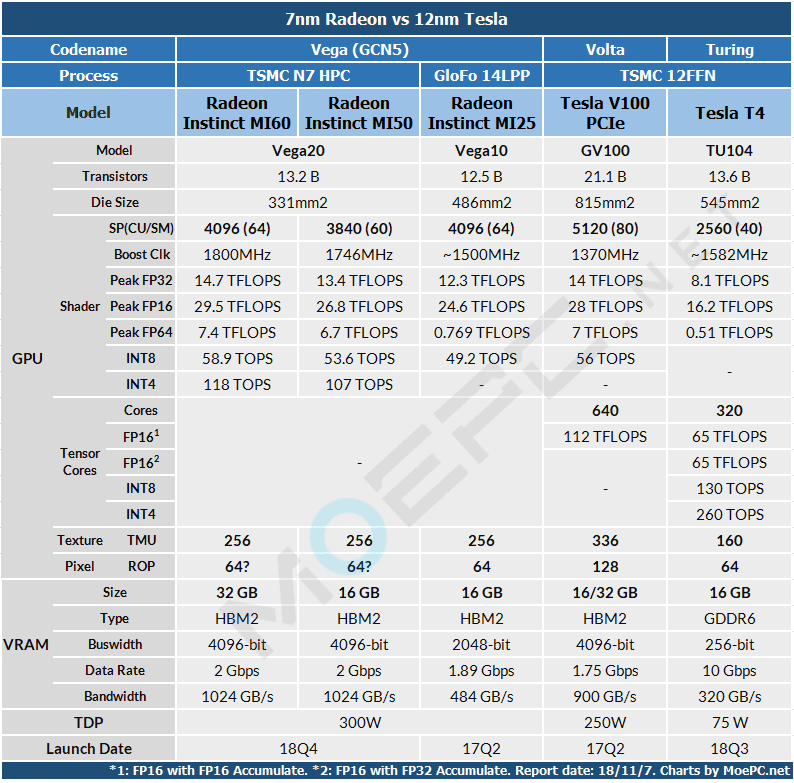

FP32性能达到14.7 TFLOPS, FP64为7.4 TFLOPS【1/2比率】,

FP16:29.4 TFLOPS;

INT8:59 TOPS,

INT4:118 TOPS。

换算过来Boost频率能达到1794MHz,比Vega 10的1677MHz高了不少。平均频率大约有10%的提升。

如果和同样300W TDP的MI25对比,Vega20在多了两块HBM2的情况下,频率增加了25%。

由于主打的是HPC,TMU/ROP应该会维持同样的256/64配置。

TDP 300W。后续非旗舰型号应该能压到150-200W左右。

还有Radeon Instinct MI50,预计为Vega 20的harvested版本,性能大概是MI60的90%左右,应该是切掉了几组CU。【更新确认:MI50切到了 3840SP,4组CU,16GB HBM2,300W TDP】

Radeon InstinctMI60/MI50/MI25 和 Tesla V100 /T4的对比

Radeon Instinct MI60和MI50都可以算主推HPC和机器学习的产品;AMD还把32GB的MI60的定位拓展到GPU虚拟化市场,比如云游戏、App串流等;而显存更小定位更低的MI50进一步瞄准ML inference市场。

本文地址:http://www.moepc.net/?post=5119

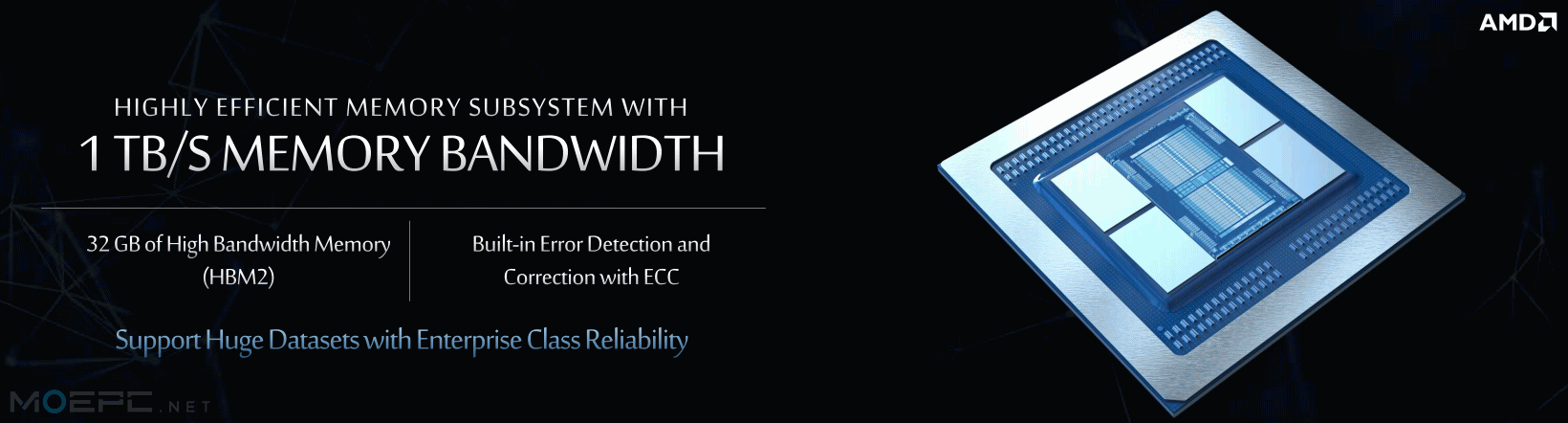

带宽则是Vega 20显著提升的另一个地方,HBM2从2块变成4块,频率2Gbps,带宽达到1TB/s。由于是企业级产品,ECC当然是支持的。是完全的ECC,包括HBM2,还有CU里的SRAM,L2等都是ECC的。

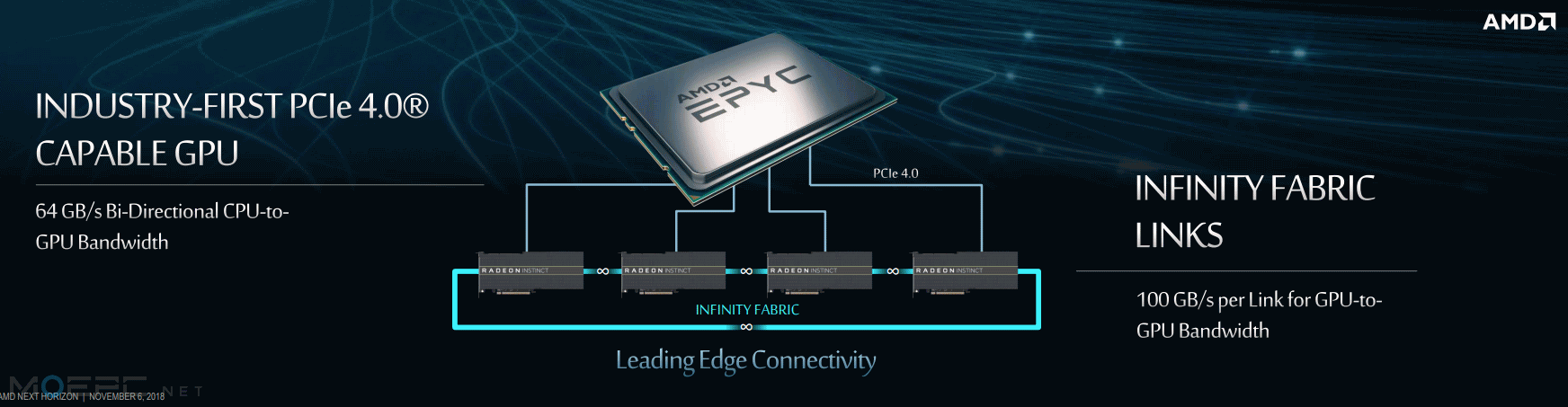

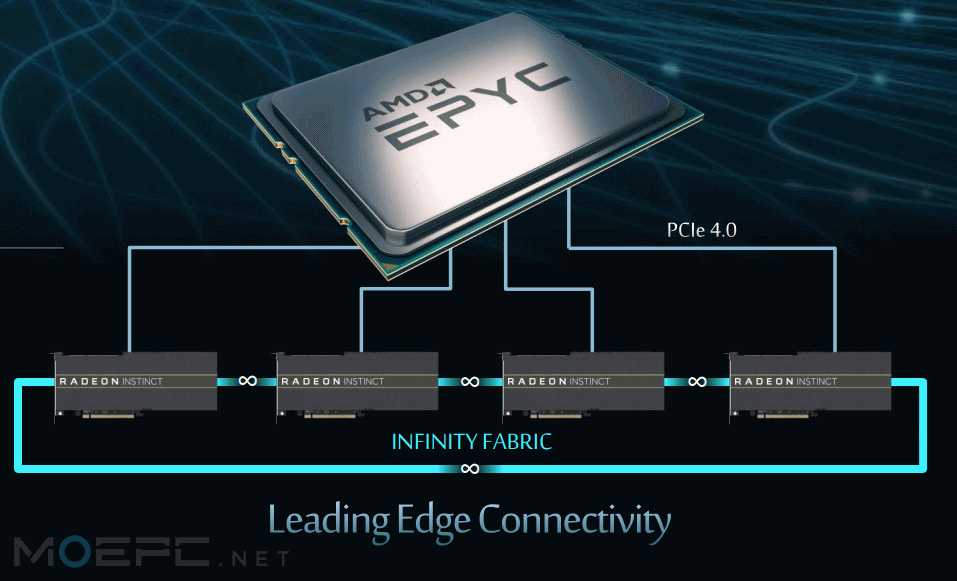

Vega 20还是业界首款支持PCIe 4.0的GPU。相比PCIe 3.0, 4.0提供双倍的带宽,双向64GB/s【CPU到GPU】。正好Rome也支持PCIe 4.0,形成一个平台。

而多个GPU之间则是Infinity Fabric Link提供互联,每条IF能提供100GB/s的GPU间带宽,组成一个环形,多GPU效率比以往更高。这个很类似NVLINK。

看样子每颗GPU应该只有两条IF,没法组成更复杂的结构,会有GPU无法直接互联。

在现场看到了4块mGPU的XGMI Link

【更新:GPU显存访问延迟只有60-70ns,延迟非常低。】

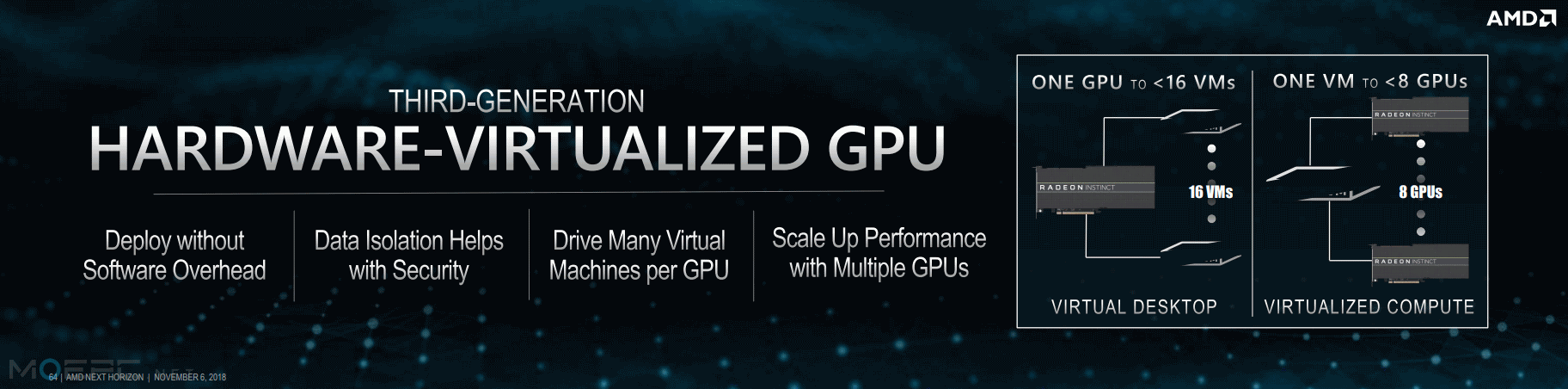

Vega 20是AMD第三代支持硬件虚拟化的GPU,硬件虚拟化没有软件的overhead,没有授权费。

单GPU可以支持最多16个VM【虚拟化桌面】,单个VM也可以分配最多8个GPU【虚拟化计算】,灵活配置。

随着Vega 20/Radeon Instinct MI60的发布,AMD也发布了ROCm 2.0。

ROCm是开源的,可以在AMD、NVIDIA的GPU上运行,也能在Intel CPU上运行。

支持最新的机器学习框架。支持Dockers和Kubernetes。

目前ROCm 2.0已经upstream给了上游的Linux内核发行组织。

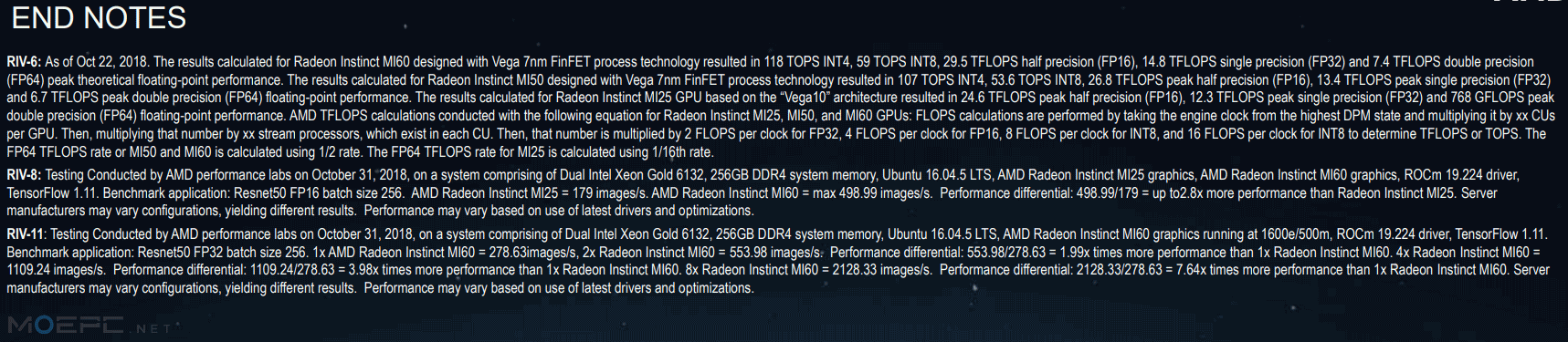

好的扯了这么多我知道你们肯定只关心性能。下面是AMD给出的官方性能数字。

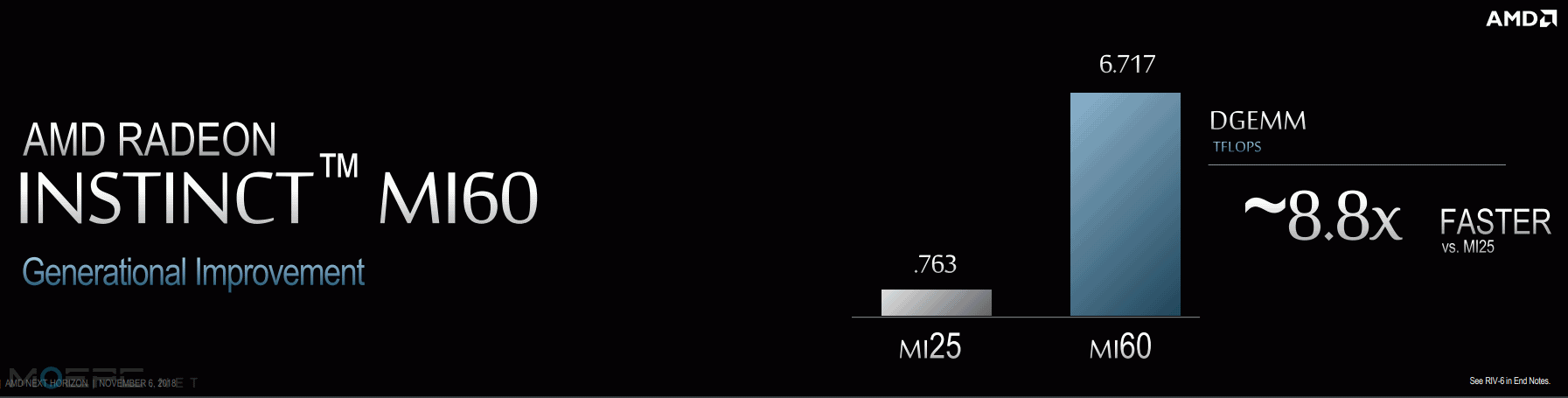

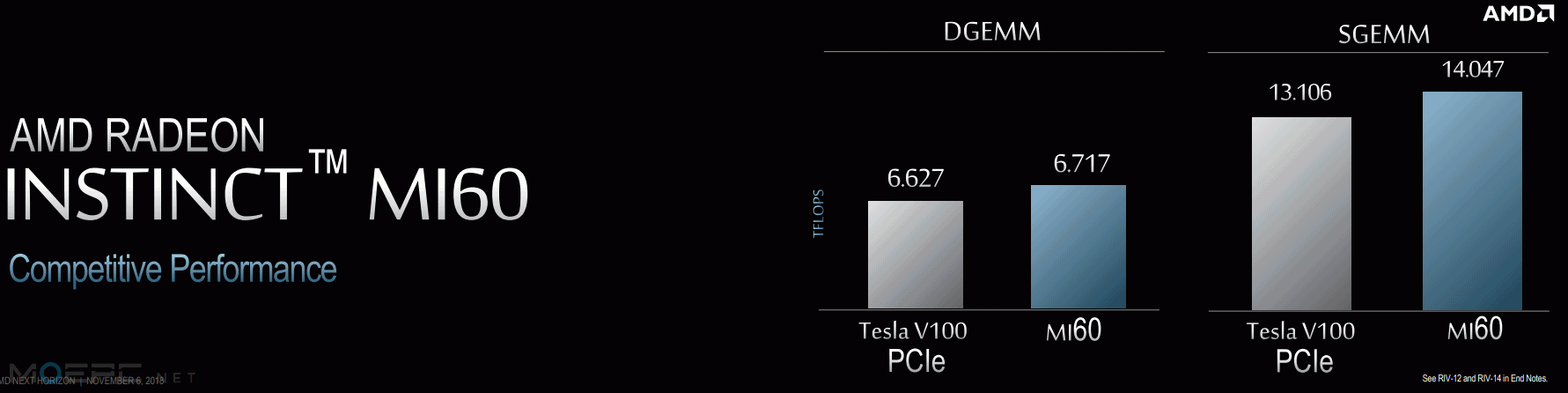

DGEMM

Vega20比Vega10在上快8.8倍

6717 GFLOPS vs 763 GFLOPS

【这是自然。因为Vega10只有1/16的FP64。不算频率的话Vega20的FP64理论性能为Vega10的8倍】

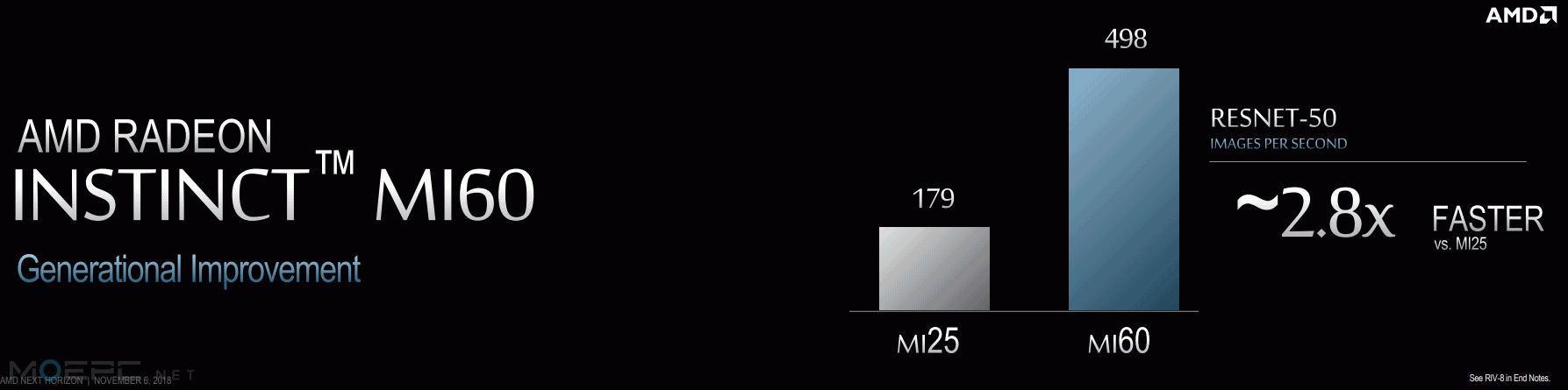

RESNET-50

Vega20是Vega10的2.8倍

498 vs 179

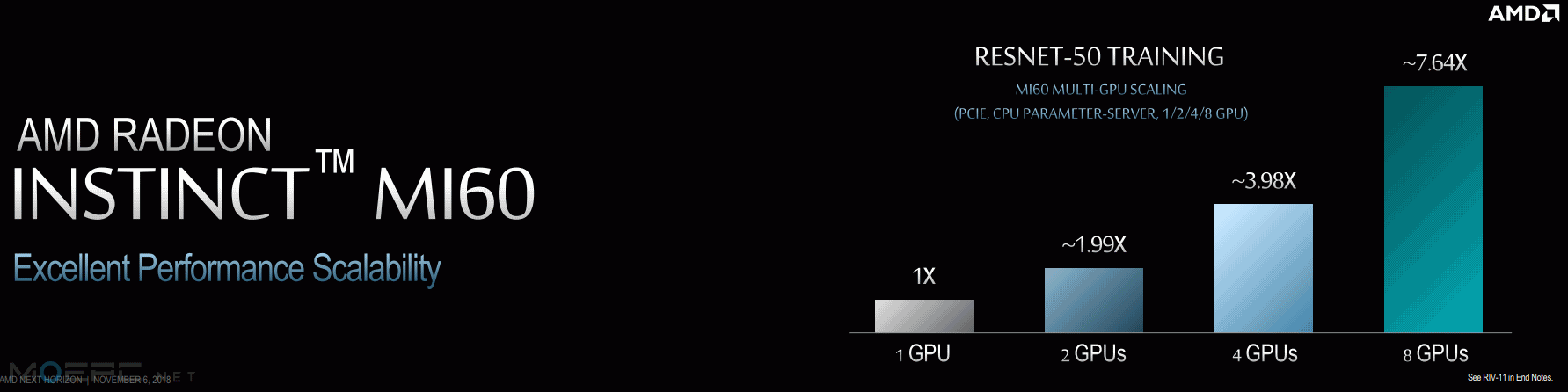

RESNET-50 TRAINING

多GPU效率

2 GPU达到1.99x【99.5%】

4 GPU达到3.98x【99.5%】

8GPU达到7.64x【95.5%】

对比Tesla V100 PCIe

双精度和单精度均强于V100

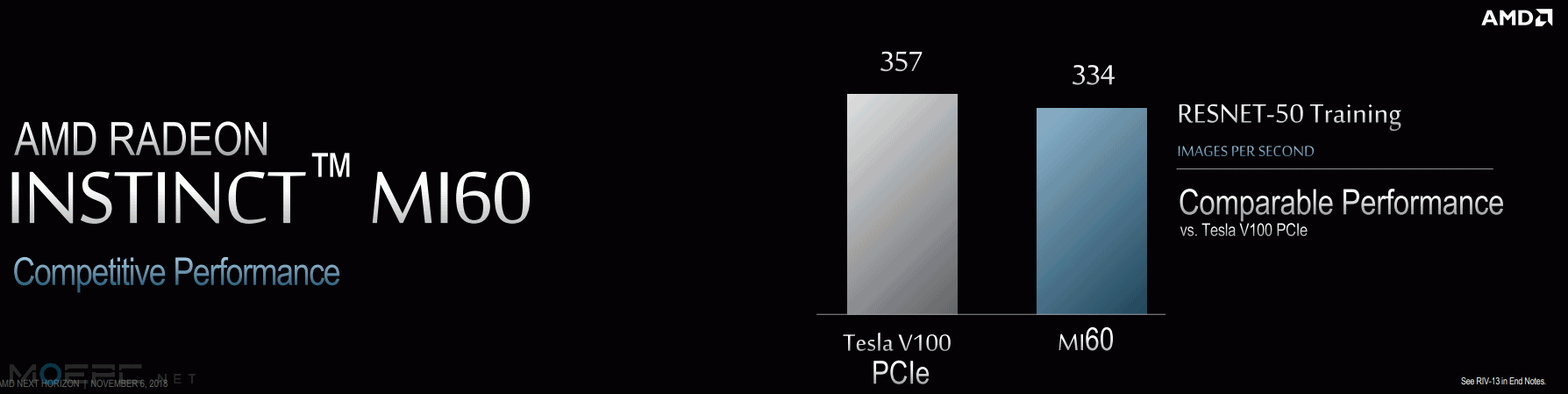

RESNET-50 TRAINING

大概为V100的94%性能

Radeon Instinct MI60将于本季度出货。

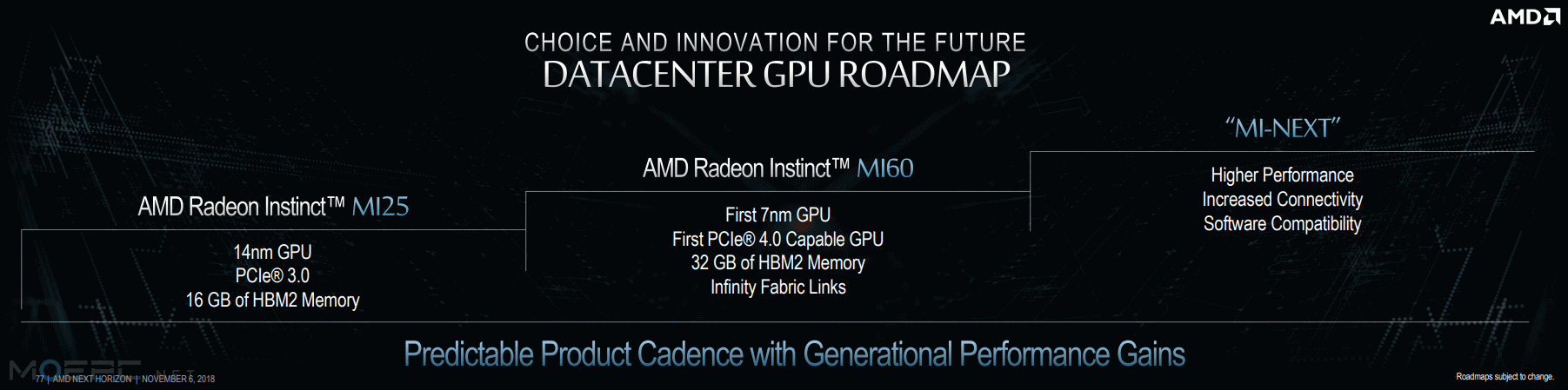

与此同时AMD还更新了数据中心GPU的路线图。

Vega20的下一代将会有更高性能,更多互联能力,更好软件兼容性。

至于名字“MI-NEXT”只是临时放在那里的占位符。

以上是本次活动关于GPU方面的所有更新。

Zen 2以及第二代 EPYC “ROME”

TSMC N7 HPC制程

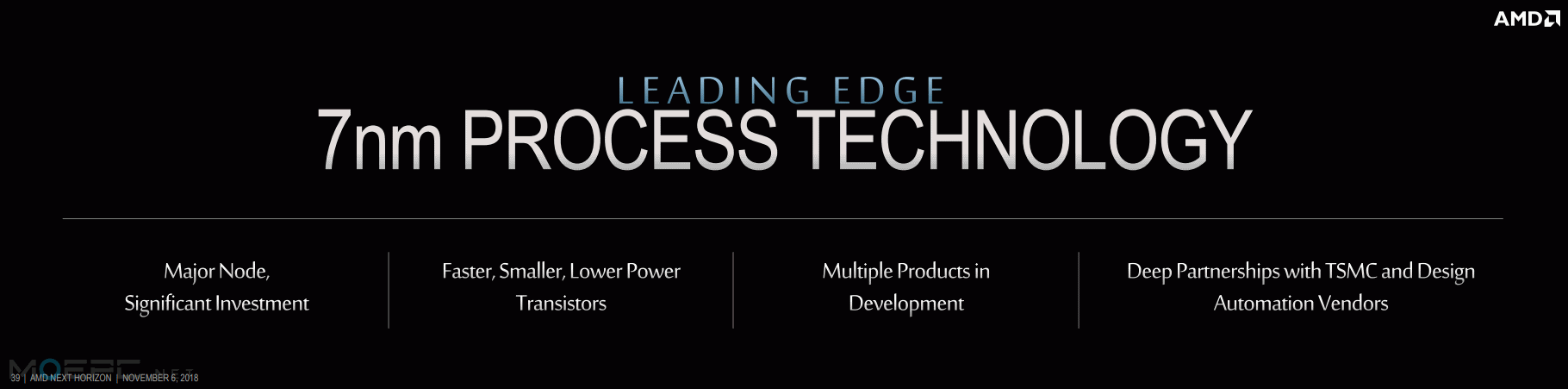

和Vega20一样,Zen2也是用TSMC 7nm HPC工艺制造的。关于N7 HPC上面Vega 20已经有讲到。

AMD在设计当初考虑到代工厂的10nm属于半节点,带来的提升不是很明显,于是把赌注都下在了7nm节点上。

相较14/16nm,7nm HPC带来两倍的密度,同等频率下功耗只有一半,同等功耗下频率达到1.25倍以上。

N7 HPC的密度比N7 SoC要低。前者为高性能计算优化,需要频率;后者注重移动低功耗领域。

AMD在Next Horizon活动上拿的应该是TSMC CLN16FF对比,密度比14LPP还要低一些。

TSMC在7nm节点的进度明显快于三星和Intel。不得不佩服台积的实力。

在Zen2的研发过程中,AMD和TSMC有着紧密的合作关系。

Zen2架构:前端及浮点大幅加强

关于架构细节方面AMD并没有提太多,信息也给的很笼统,没法进一步分析。

个人不会没有事实依据就去预测。

如果有新的消息会第一时间更新。

作为世界上首款高性能x86 7nm CPU,Zen 2架构带来了各方面的显著提升。

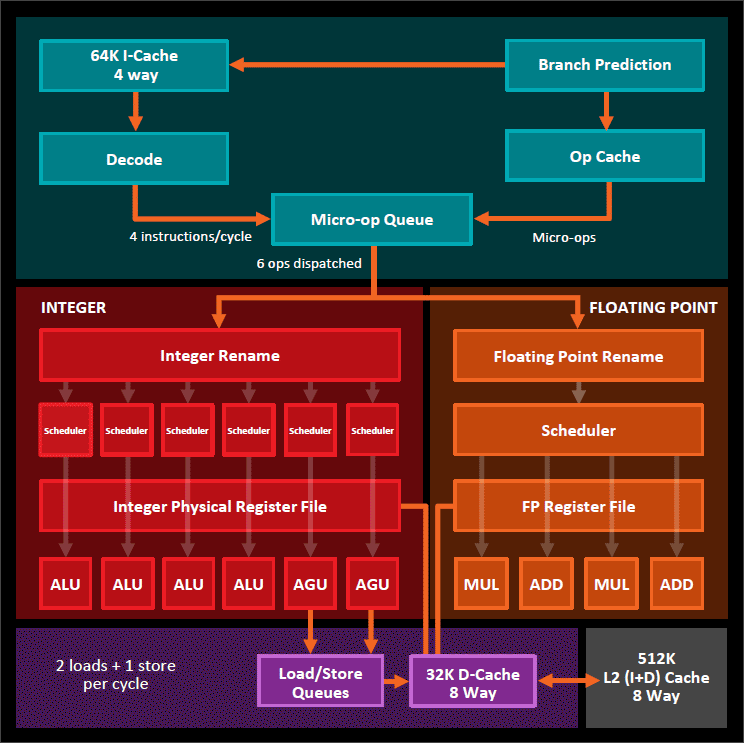

总的来讲,Zen2在性能方面改进了如下几点

- 改进了执行管线

- 浮点和Load/Store翻倍

- 核心密度翻倍

- 单次运算耗能减半

Zen2的输出能达到Zen的两倍,IPC也有明显提升。

AMD内部用DKERN + RSA测试,Zen2的IPC为4.53,Zen的IPC为3.5,Zen2在这里比Zen高29.4%。

【18/11/14更新:关于这个IPC测试AMD给出了进一步的声明:

“As we demonstrated at our Next Horizon event last week, our next-generation AMD EPYC server processor based on the new “Zen 2” core delivers significant performance improvements as a result of both architectural advances and 7nm process technology. Some news media interpreted a “Zen 2” comment in the press release footnotes to be a specific IPC uplift claim. The data in the footnote represented the performance improvement in a microbenchmark for a specific financial services workload which benefits from both integer and floating point performance improvements and is not intended to quantify the IPC increase a user should expect to see across a wide range of applications. We will provide additional details on “Zen 2” IPC improvements, and more importantly how the combination of our next-generation architecture and advanced 7nm process technology deliver more performance per socket, when the products launch.”

跟我说的一样,这个29%的IPC提升只是AMD内部跑的这个程序有29%的IPC提升,不代表其他类型的程序会有一样的结果。Zen架构的特性之一就是浮点+整数指令混合执行能达到最大指令吞吐量,29%属于比较理想的情况。

如果说平均IPC的话,个人的预计不会有30%这么高,10-15%差不多。

纯浮点提升会比较明显,整数相比之下提升就比较小。

但个别跑AVX的程序里可能会有远高于29%的性能提升。】

由于是浮点和整数混合测试,属于比较理想的情况。

如果能用上AVX的测试的确会有很大提升,因为Zen2主要加强的还是浮点性能。

本文地址:http://www.moepc.net/?post=5119

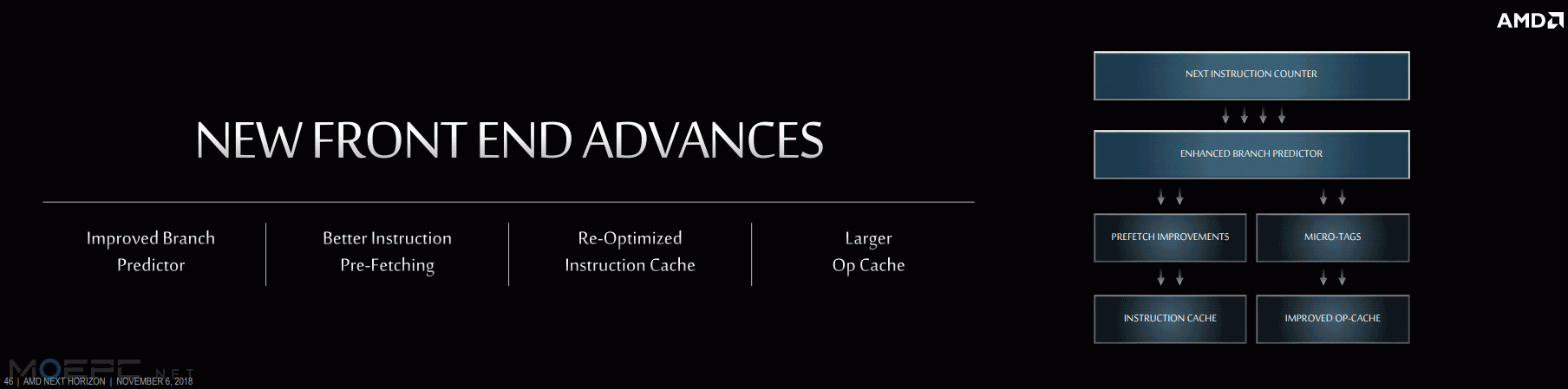

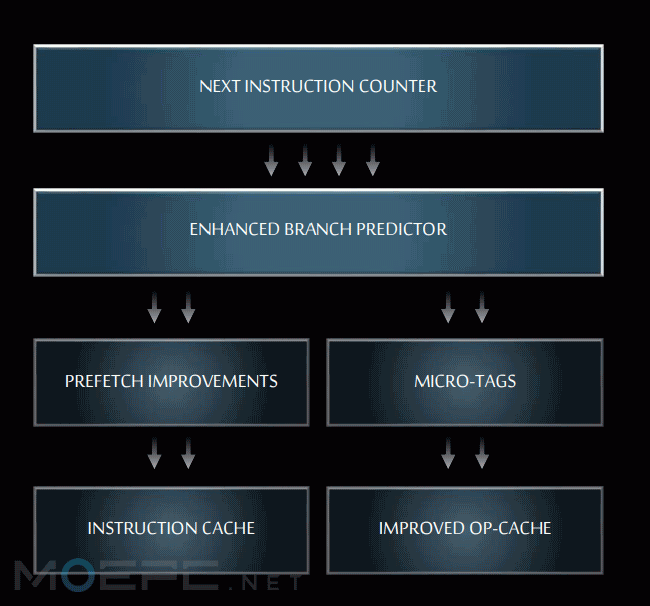

首先是前端的改进:

- 改进的分值预测单元

- 更好的指令预取

- 重新优化指令缓存

- 更大的微指令缓存

这点显得尤其重要,因为Zen的前端被认为是最大的瓶颈之一。

改进的前端能够保证Zen2充分利用加强的后端处理管线,减少管线的等待时间。

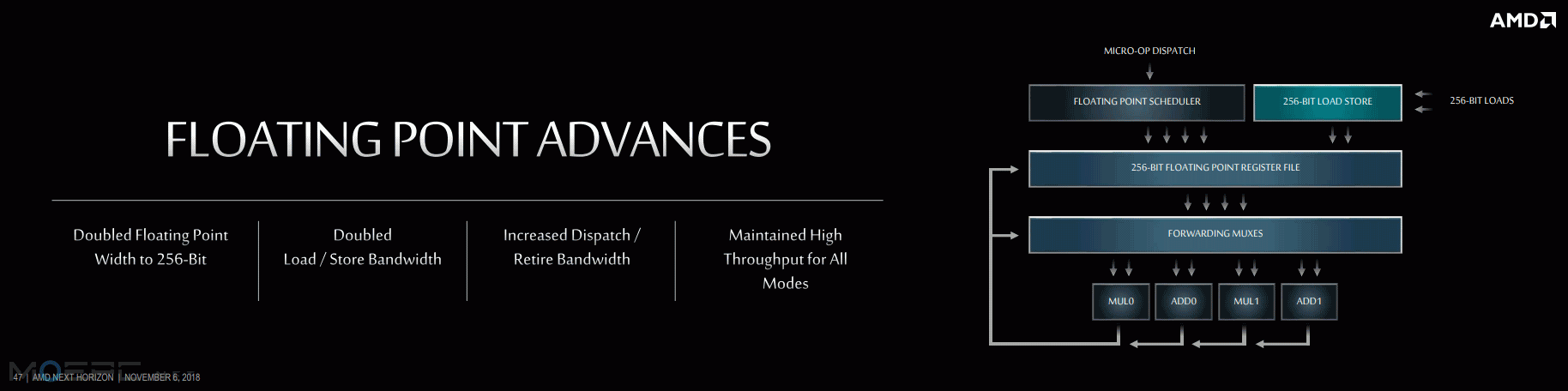

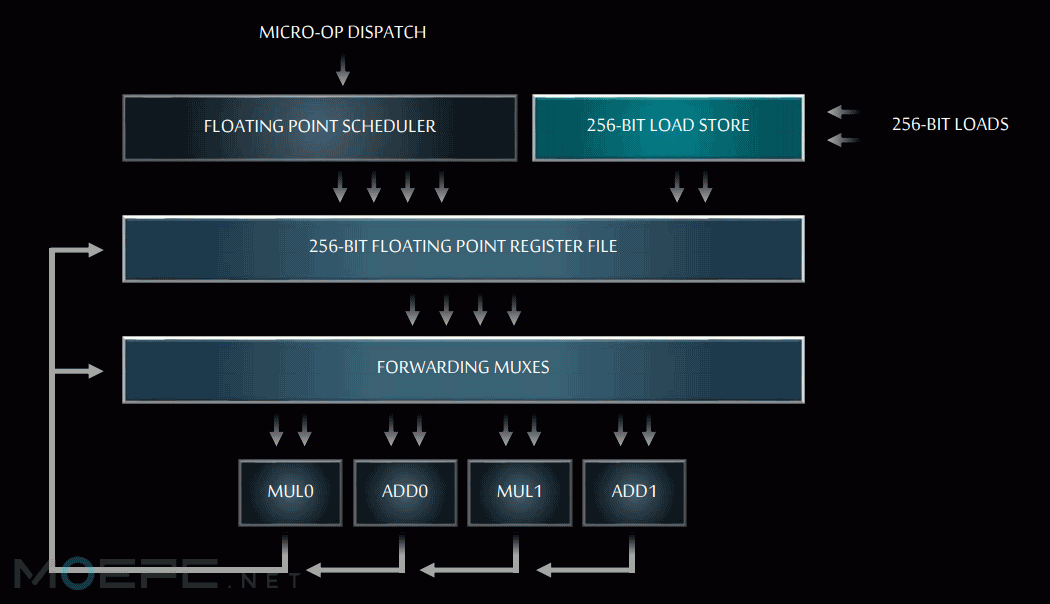

浮点单元也得到了大幅加强,基本翻倍。

- 依然是4个浮点单元,2MUL+2ADD,但指令宽度从128-bit翻倍到256-bit

- Load/Store带宽翻倍

- 增加Dispatch/Retire带宽

- 各种模式下均能保持高输出

Papermaster说,AMD不是仅仅将FPU指令宽度翻倍,而是把前端的Load/Store也翻倍到256-bit,保证能在实际应用中看到性能提升。增加的dispatch/retire带宽还能让Zen2的FPU更高效地运行非矢量程序。

当初AMD设计把Zen的FPU设计成128bit就是因为当时【现在也是】的绝大多数程序依然只用得到128bit浮点指令,所以设计了非常高效的128bit FPU,结果也很成功。

Zen2则是这一设计决定的一次进化。保持架构的平衡。

对比Zen

关于Zen架构的分析详见:Agner:AMD Ryzen 架构及指令输出、延迟测试结果

http://www.moepc.net/?post=1805

同时还有安全上的加强。原本Zen架构就不受Intel架构专属漏洞Meltdown等的影响,在安全考虑上要强那么一点。

现在Zen2则更进一步,在硬件上加强Spectre漏洞的修复。

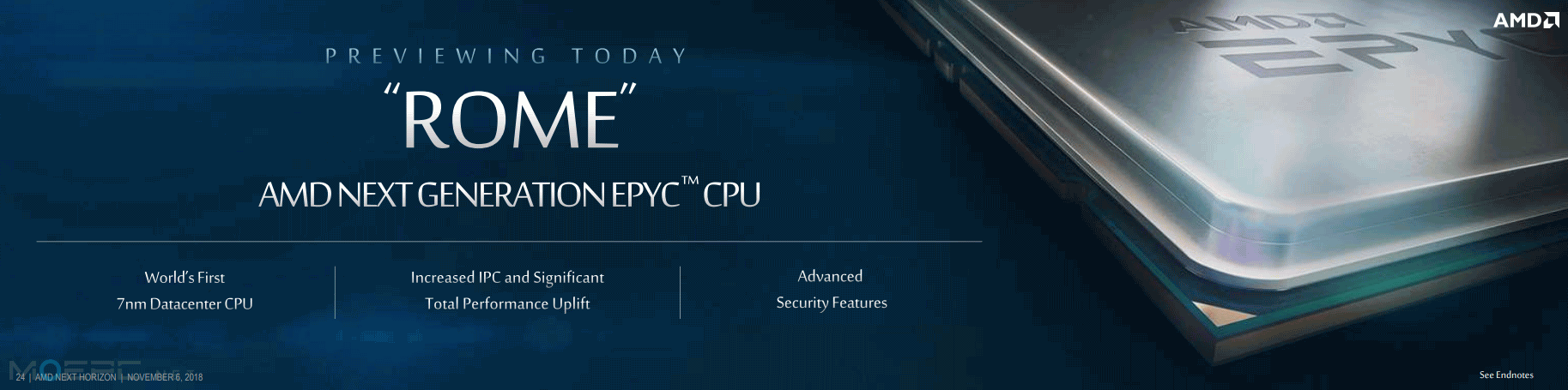

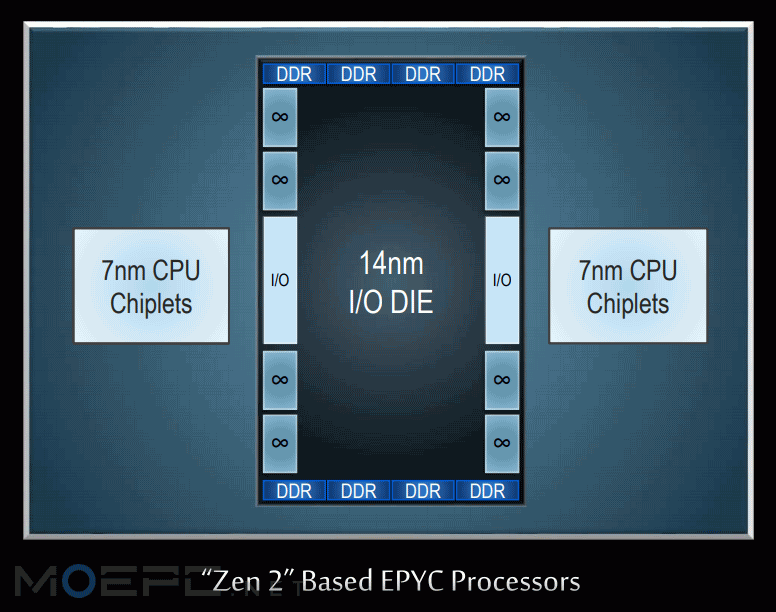

基于Zen2架构的EPYC,代号“Rome”

这个才是本次发布的重头戏,也是很多人最关心的。

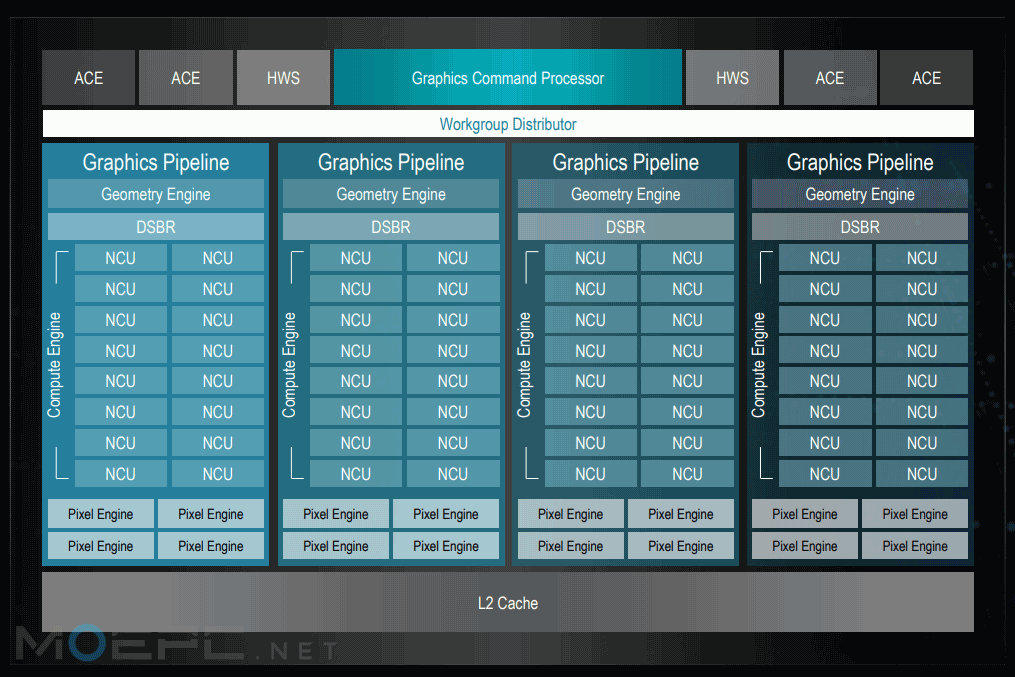

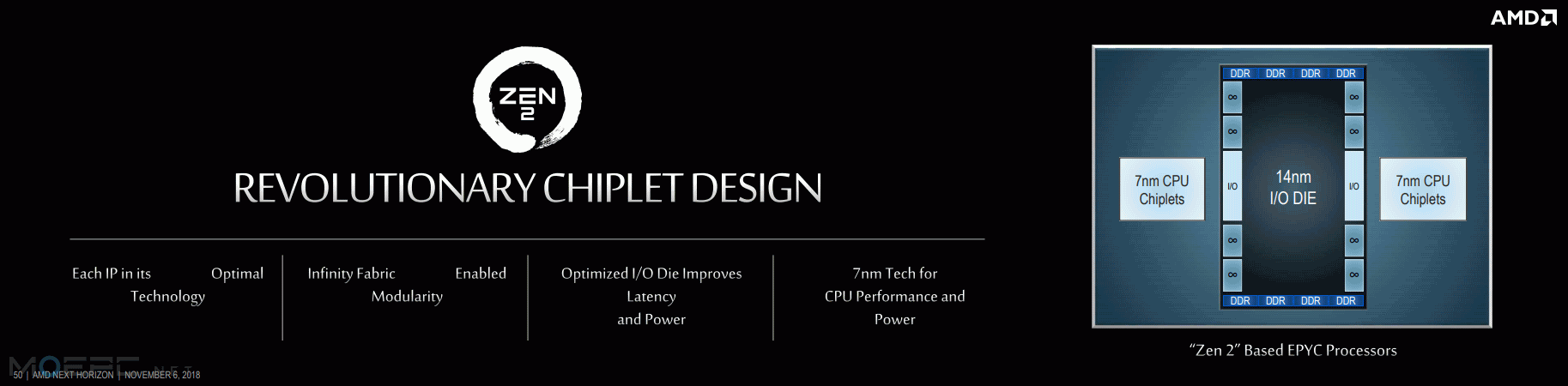

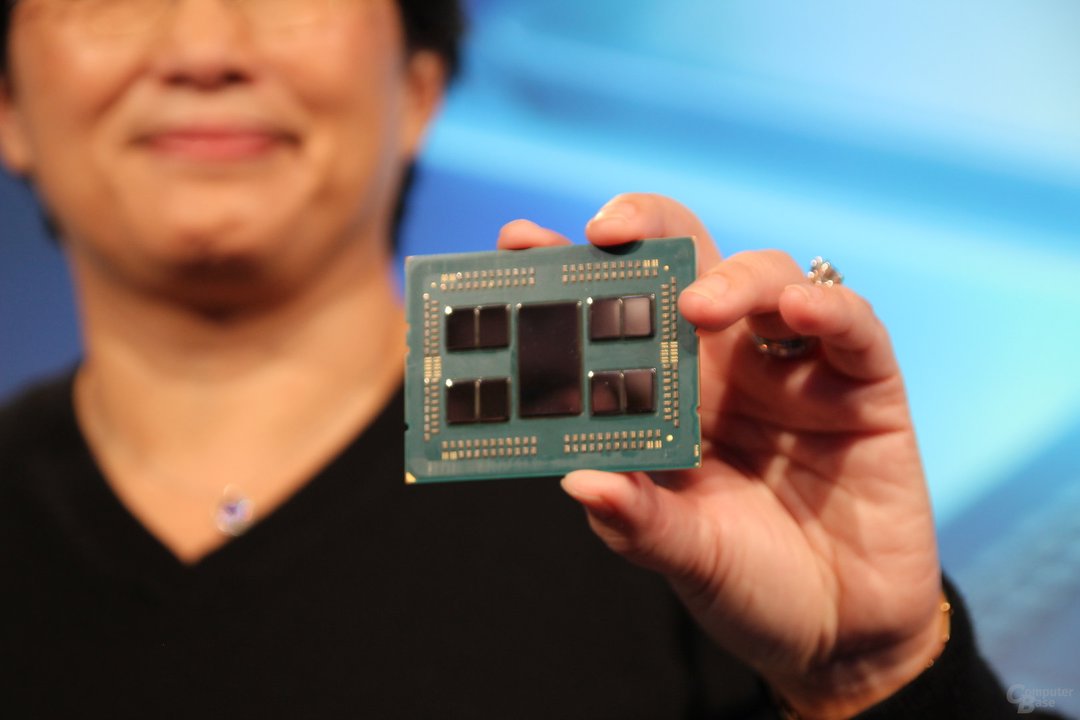

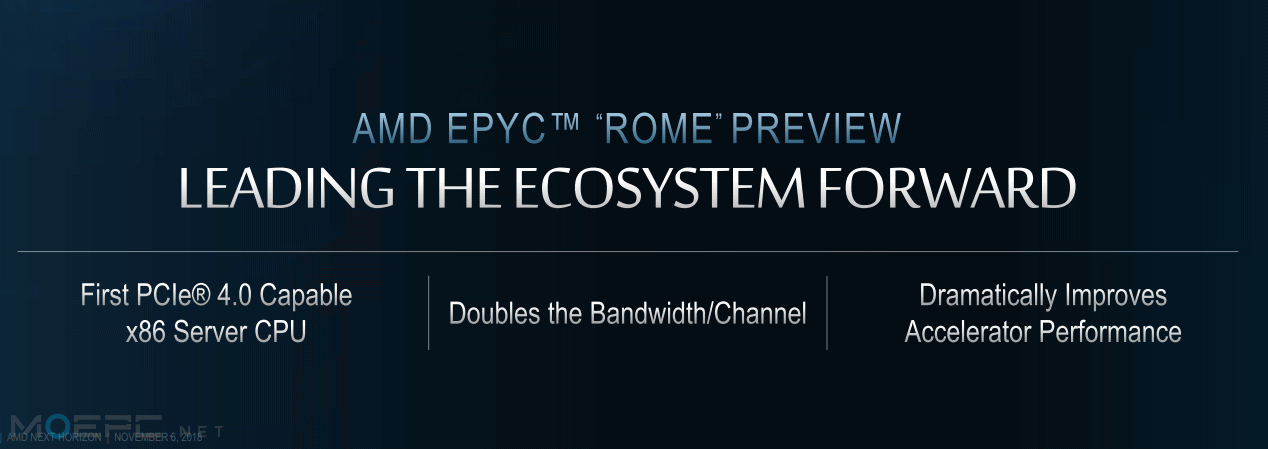

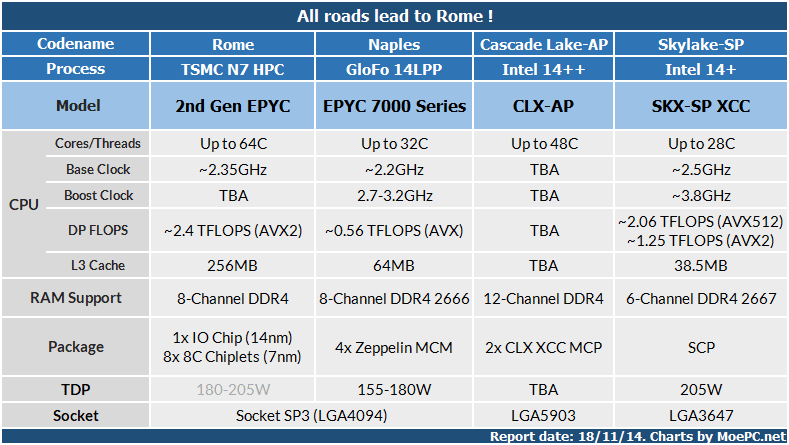

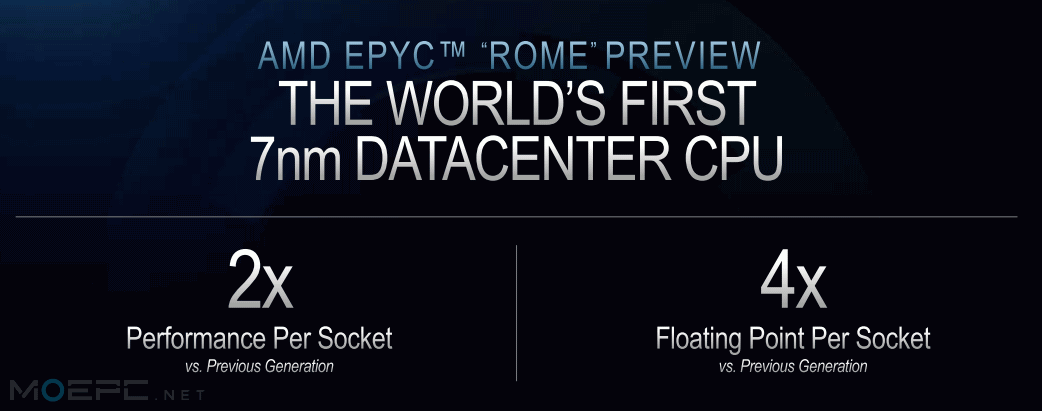

第二代EPYC处理器,代号”Rome”,单路将提供最多64核心,8通道DDR4,单路4TB内存,128条 PCIe4.0支持,更高的IPC,256MB L3缓存。单路输出达到Naples的两倍,浮点输出达到四倍。

7nm HPC制程,世界首先。Intel的10nm服务器得等到2020下半年。

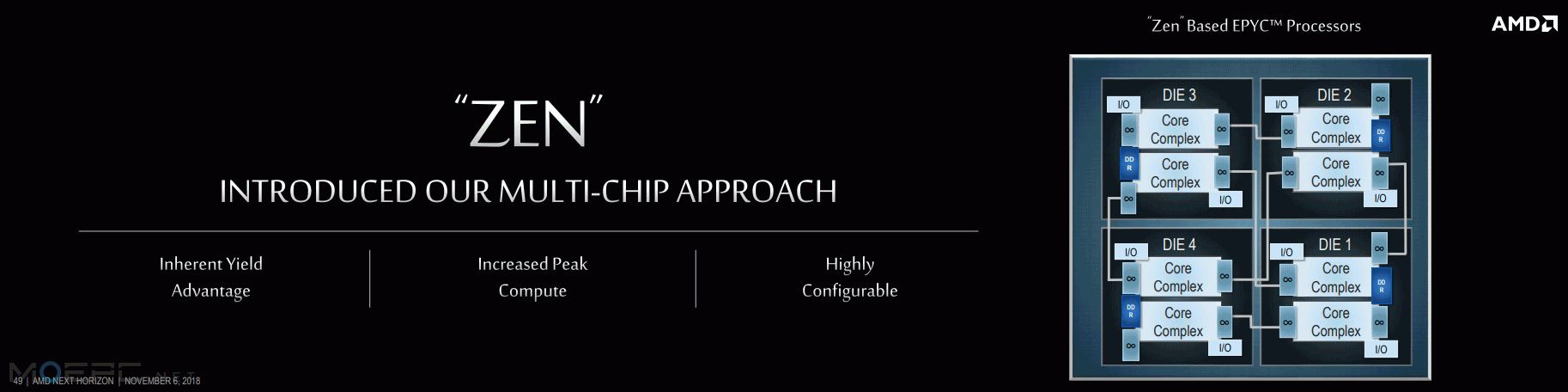

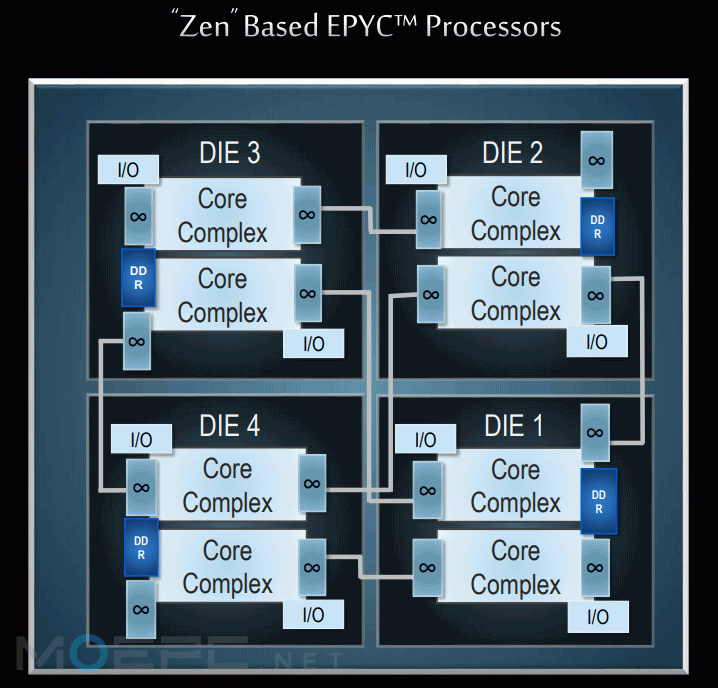

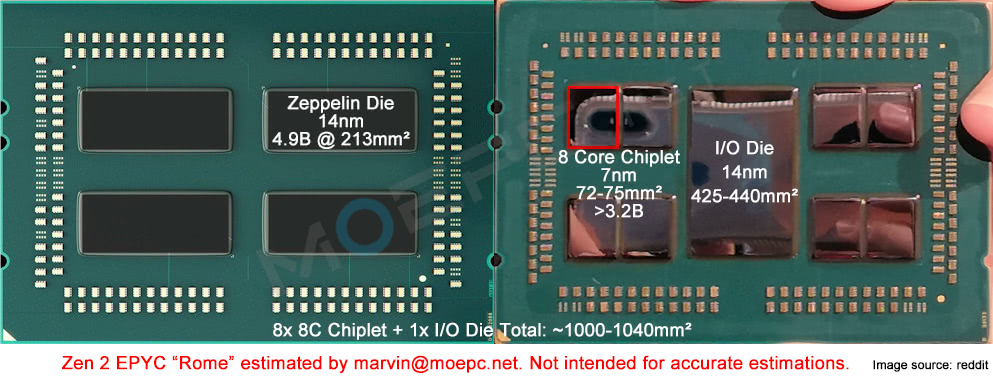

都知道第一代EPYC用的是4x MCM,4块Zeppelin die用IF连接,成为AMD服务器平台的基石,在良率和密度上均有优势。

而第二代EPYC进行了大刀阔斧的改革,利用第二代Infinity Fabric,将I/O部分分离成一颗独立的I/O die,使用14nm制程制造,位于封装中心;周围则是8颗7nm的CPU核心chiplet,每颗包含8个Zen2核心。【Zen架构Zeppelin也是每颗die 8个Zen核心,2x 4C CCX。至于Rome的8C CCX目前还没有确认。Next Horizon会后有人问了这个问题,AMD没有直接回答,说更详细的架构信息会在后续发表。

跟我之前说的一样,已经证实Rome依然是2x 4C CCX。】

I/O die集成了很多东西,面积巨大,大概有440mm2左右,良率不会太好看。

【我也好奇AMD在IO die里还塞了些啥,大部分可能都被IMC占了

简单的小学数学:IF、IMC、IO这些玩意在Zen上占了将近一半面积,4块就是400mm2。这些东西是很占面积的。

Rome大概率不会在I/O Die上集成缓存。

Milan可能吧。只是可能。

拿eDRAM做成L4比较合适。Intel 22nm 128MB的Crystal Well只有84mm2。】

但这是服务器用的,比起服务器的margin来讲这点成本就不算高了

桌面AM4如果沿用同样的Chiplet,就需要集成一个更小的IO die,切成四分之一。

7nm的CPU chiplet和I/O die之间采用点对点的IF连接【互相通信需要通过IO Die】,IMC和I/O都在I/O die上。

两颗7nm的CPU chiplet比一颗14nm Zeppelin还要小。

粗略计算两颗7nm CPU Chiplet的封装面积是单颗14nm Zeppelin的68%。

单颗7nm CPU Chiplet的封装面积是单颗14nm Zeppelin的32%。

当然CPU chiplet也就去掉了IMC、IO等等IP模块。L3缓存从Zeppelin的16MB翻倍至32MB。

像CPU核心、缓存这些逻辑元件能用7nm制程大幅缩小,某些IP模块则从中收益不大。

Rome的设计就是将正确的制程用在正确的地方。

实物图 图源:computerbase.de

这样能够达成更低延迟,更低功耗,弥补第一代EPYC “Naples”上出现的部分不足。

Rome也是首个支持PCIe 4.0的x86服务器CPU,一共128条。PCIe 4.0带来64GB/s的双向带宽,相比3.0翻倍,对于加速卡等的性能发挥很重要。

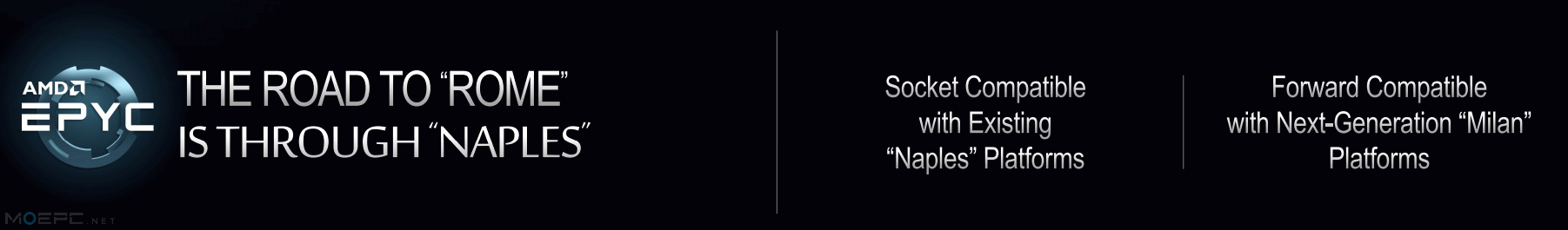

兼容、升级性:Rome向后兼容目前的Naples平台 ?? Socket SP3 LGA4094,

同时向前兼容Zen3架构的第三代EPYC,N77nm+工艺的Milan。【更新:AMD还在看三星7nm EUV 7LPP的性能如何,目前尚未确定工艺。】

当然,如果用Naples的老平台就没法用PCIe 4.0咯

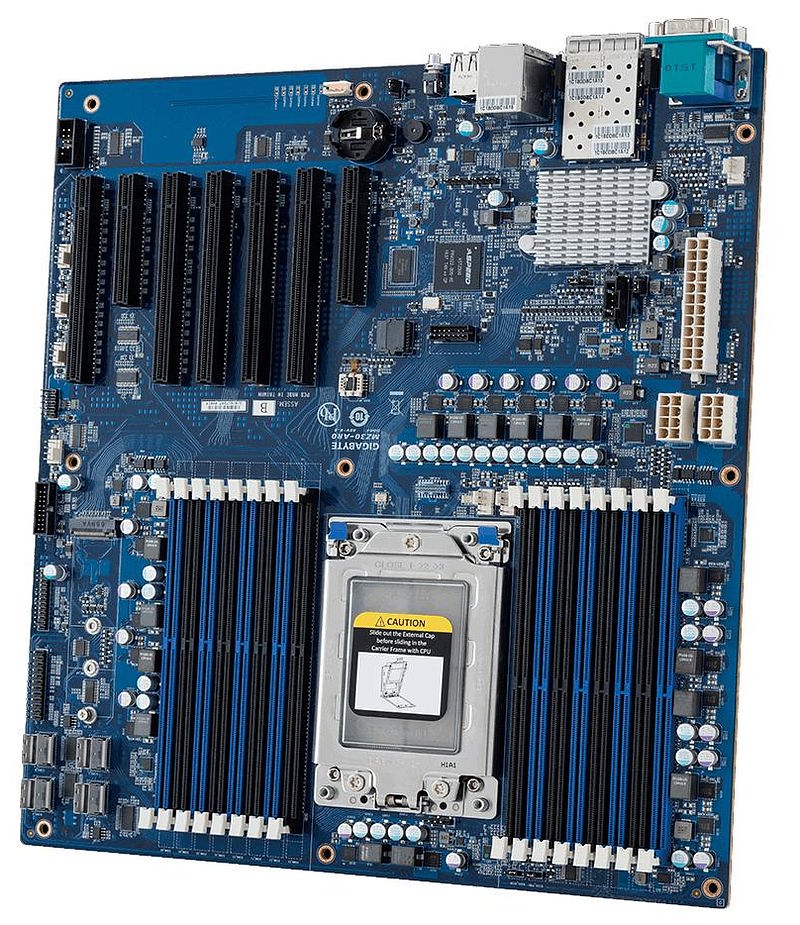

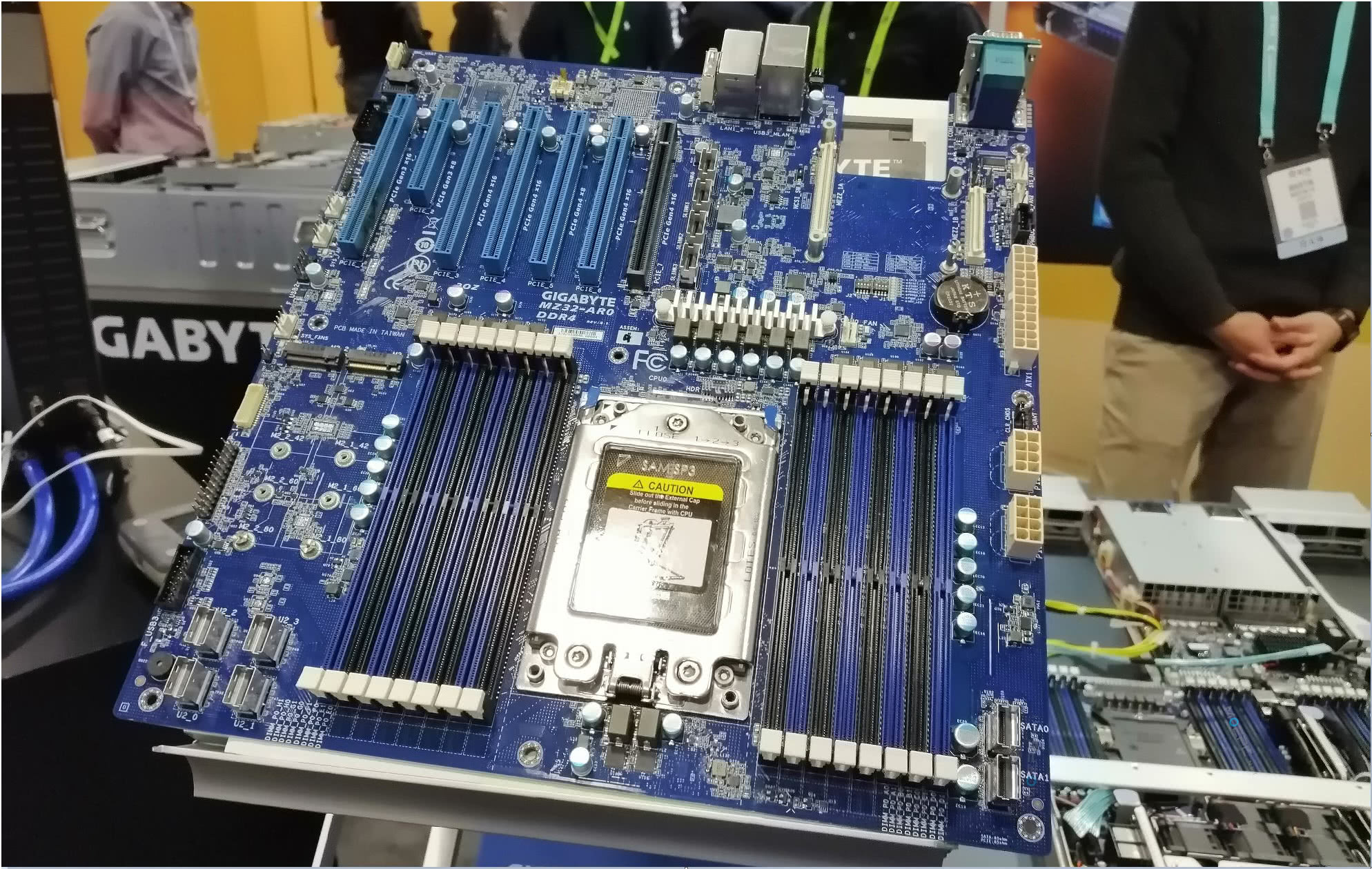

18/11/14更新:在SC18现场的”Rome”原型单路主板图

技嘉的MZ32-AR0

目前在售的Naples的相应型号为MZ30-AR0和MZ31-AR0

可以看到大致布局和MZ31-AR0基本相同

只是有5条PCIe x16插槽升级为了4.0

“Rome”平台和”Naples”平台互相兼容,要兼容的话供电需求就不能有多少变化。预计单路高核心数 Rome的TDP在180-205W左右。

图源:stocktwits.com

这个是MZ30-AR0

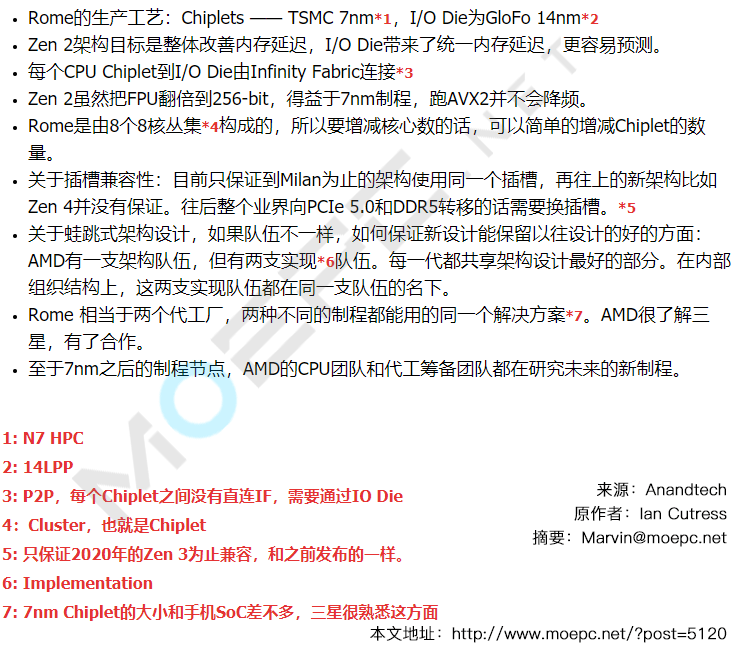

【18/11/13更新:Anandtech和AMD CTO Papermaster的访谈中提到了一些新信息,这里是摘要:

http://www.moepc.net/?post=5120

本文地址:http://www.moepc.net/?post=5119

All roads lead to Rome !

N7 HPC密度、Zen2芯片面积相关分析

看到某低能拿着Vega20预测N7 HPC的密度,觉得很有必要说明一下。

大致的我上面已经说到了,Vega20并不能很好地代表N7 HPC的密度,这里不再重复。

当然我也不会像某些人张口就来IO Die“600mm2”之类的话。

本人只会根据已有事实,要有数据支撑再进行合理的推断。

首先,根据现场照片粗略估算:单个8C 7nm Chiplet的面积大概在72-75mm2,I/O Die大概有425-440mm2。整个”Rome”的8颗Chiplet + I/O Die 大概在1000-1040mm2。

14LPP制程下单个Zen CCX面积为44mm2, 目前已知的Zen2改进点主要是前端、浮点和L3

好的下面开始胡扯:

前端和浮点这一堆东西占了单个14nm Zen核的将近60%面积。单颗Zen核面积为7mm2。

如果算上Zen2的各项改进,保守估计:4个 Zen2核心+L3 在14nm下大概需要67-70mm2,8C+L3 就是134-140mm2,大概30-32亿晶体管。

这还是只算了8个Zen2核心+32M L3,不算目前未知的其他改进和其他chiplet内的模块的结果。

用N7 HPC 做到70+mm2,密度你说是多少?的确接近AMD官方说的最高两倍。

AMD把能充分7nm密度优势的东西都放进chiplet了。

此外,如果同样的chiplet拿给AM4用,把IO Die切成四分之一:

两个7nm Chiplet = 140-150mm2

AM4 IO Die = 100-110mm2

一共240-260mm2,没比Zeppelin大多少。

显然Zen 2 AM4上16C【比如Ryzen 7 3700X】是可行的,但并不代表AMD就100%会这么做。

如果在IO Die上集成两套不同的IMC还能继续兼容现有平台,不用改动Chiplet,对有效利用设计资源有很大的帮助。【比如Skylake就集成了DDR4和LPDDR3/DDR3L的两套IMC】

现在Client端的DDR5定档2020,大概只有Zen3才有希望支持吧。

预测终究是预测,没法做的很精确,总比毫无事实依据的异想天开要好。】

性能如何?

这次AMD在现场小小演示了一下64核 Rome的性能。

理论上Rome的单路输出是Naples的两倍【因为有两倍核心】

浮点输出是Naples的四倍【因为有两倍核心x两倍浮点宽度】

但理论终究是理论,实际性能只有测了才知道。

在现场AMD用Cray 4K测试,对比目前Intel的最强Skylake-SP系统和AMD的Rome

Cray是Linux上常用的浮点性能测试。【AMD说测试用的是AVX2】

Intel:双路白金至强 Xeon-SP Platinum 8180M, 56C/112T,3TB DDR4

AMD: 单路 Zen2 EPYC “Rome”, 64C/128T, 4TB DDR4

结果单路Rome用时28.1秒,双路白金至强8180M用时30.2秒。

双路打单路,结果单路更快。

而且Rome用的是风冷、未超频、频率还不是最终版的原型系统。

btw: 双路白金至强性能是比Cascade Lake-AP要强的。而且Cascade Lake-AP的功耗注定了要水冷。

仅凭Cray一个测试无法完全判断性能到底如何,AMD作为厂商当然会选对自己有利的测试进行demo。

不过还是很震撼。性能上优势巨大,更不用提能效。

P.S. AMD在后面又给看了一个DEMO,也是CRAY,用的应该是AVX2【AMD的人这么说的】。

双路Skylake-SP 8180M vs 单路64C Rome vs 双路Naples EPYC 7601

双路 8180M用时30.5秒

双路 7601 用时28.4秒

单路 Rome 用时27.7秒

第二代EPYC “Rome” 将于2019年发布。随着发布的临近,会有更多的信息更新。

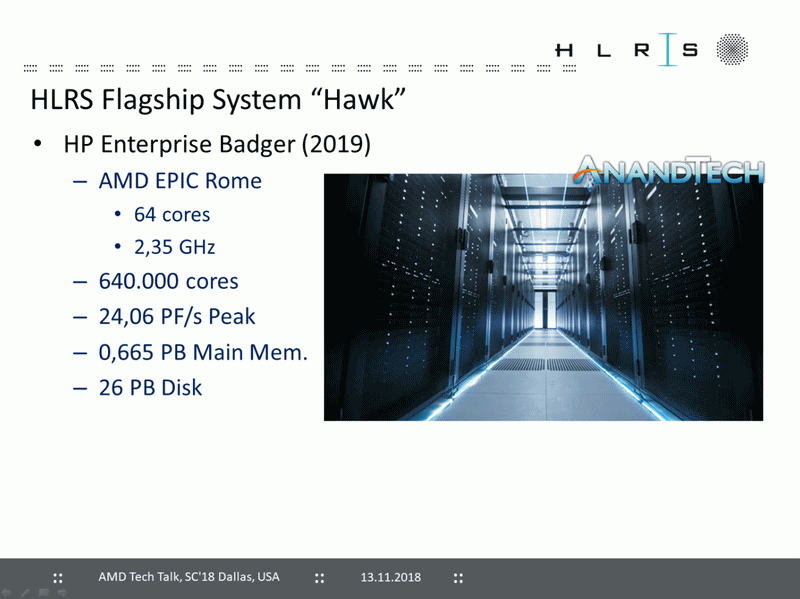

HLRS的“Hawk”超算将采用“Rome” 64核处理器,曝光“Rome” 频率及性能信息

18/11/14更新:这则发布也发表于SC18大会,由于关联度很高就一起放在这里

HLRS的“Hawk”超算将采用“Rome” 64核处理器,共10000颗,合计640000个Zen 2核心,双精度算力24.06PF/s (DP)。

算下来每颗 “Rome” 跑 AVX2 双精度性能能有2.4 TFLOPS!

Skylake-SP顶级的白金至强 8180 AVX512 DP性能为2.06 TFLOPS【AVX512会大幅降频】

AVX2 DP性能为1.25 TFLOPS

Cascade Lake-SP在这方面不会有明显提升,Cascade Lake-AP单路由两颗Cascade Lake-SP MCP组成,最高48核心,CLX-AP在AVX512双精度上会胜过Rome,只是 1.功耗爆炸 2.需要水冷。

主频2.35GHz,应该是基础频率。在核心数翻倍的情况下比EPYC 7601还要高7%,要知道两者的供电规格相近,Rome兼容现有的Naples平台,TDP大概在180-205W范围。

图源:anandtech

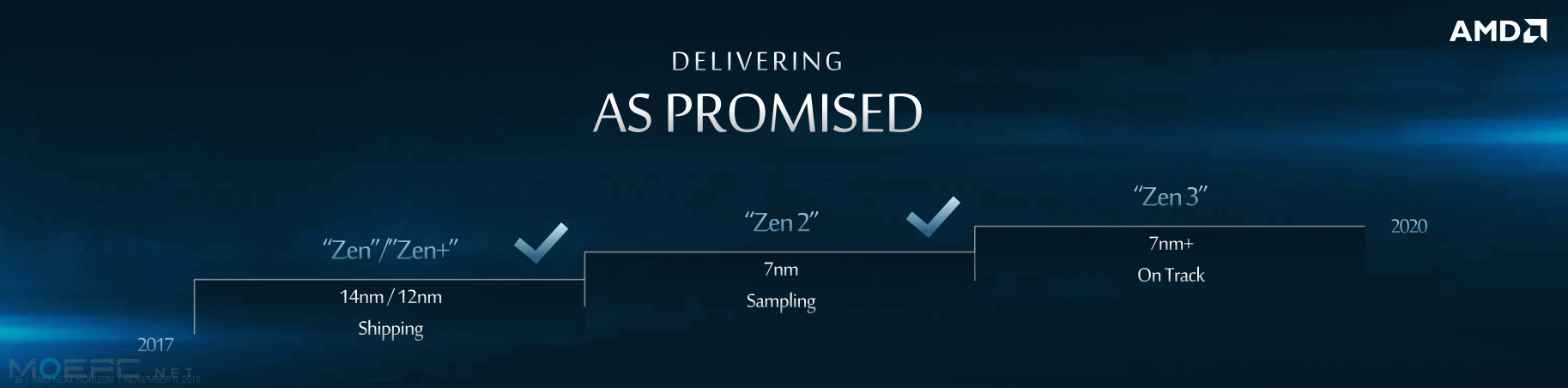

EPYC路线图更新,Zen4研发中

发布会一开始Mark Papermaster就提到Zen2和Zen3的进度一切正常,Zen3 On track。

这里强调了路线图的稳定性,“AS PROMISED”,颇有一番讽刺隔壁的意味。

Papermaster称设计队伍采用蛙跳式的策略,始终有两款架构在研发中。

与某些谣言网站所称的恰恰相反,AMD并没有跳过Zen4。【从来都没有。】

现在Zen2已经开始出样,后面就是Zen3 Milan和Zen4了。Zen4目前还处于设计阶段。

以上是本次活动关于Zen2的所有信息。

亚马逊AWS部署EPYC主机

看来财报上说年底前的4-6%市占率的确有可能啊。。

AMD 2018Q3 财报新信息http://www.moepc.net/?post=5115

据AMD预测,2021年之前数据中心的TAM将达到290亿美元

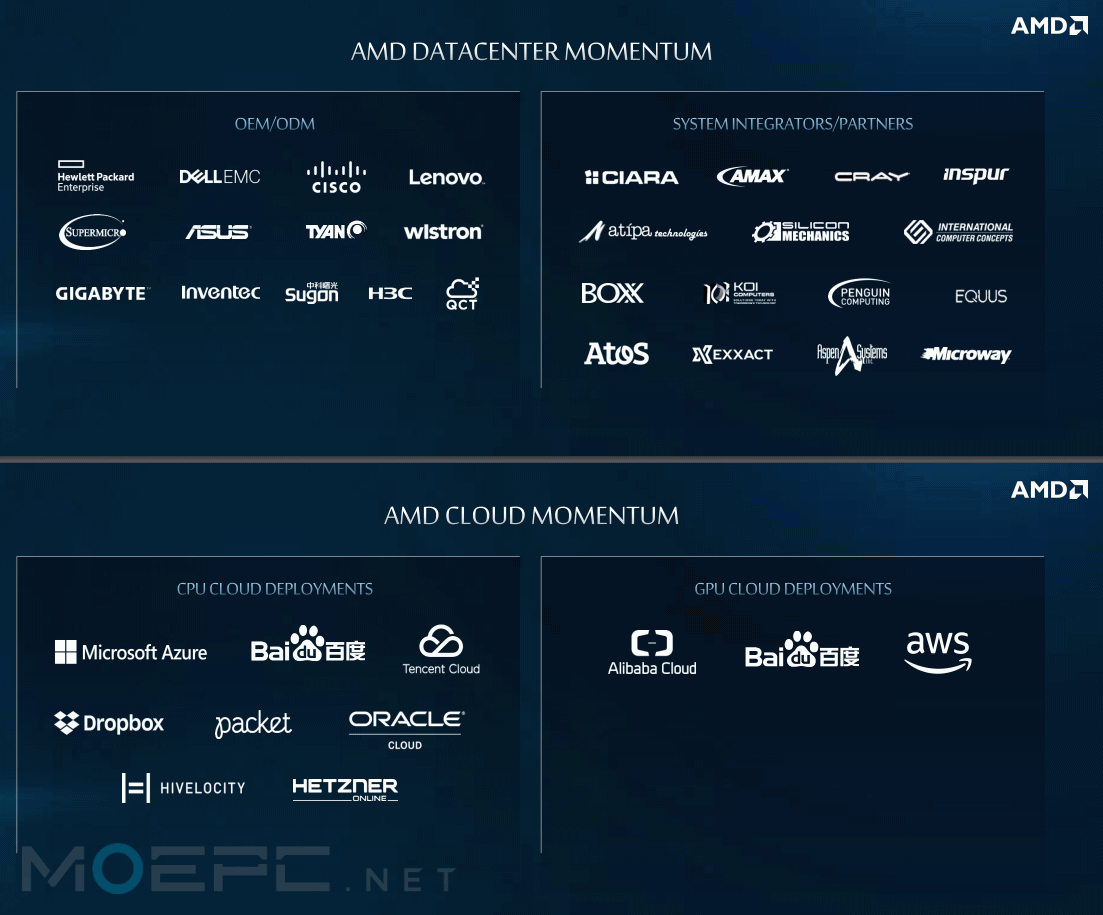

AMD去年发布的的EPYC服务器和Radeon Instinct加速卡被业界采用的情况

早在去年就发布的EPYC平台,由于企业级领域和普通消费级不同,需要很长的验证周期,所以直到最近才能看到有各种大客户采用的消息,比如Dropbox,微软Azure,甲骨文等。

AMD想让最多的用户能接触到EPYC,所以就需要和行业老大合作。而云服务行业的No.1 当然还得是亚马逊AWS。

AMD宣布亚马逊AWS将在亚马逊EC2云服务器上部署EPYC平台。这对AMD EPYC平台而言意义重大。

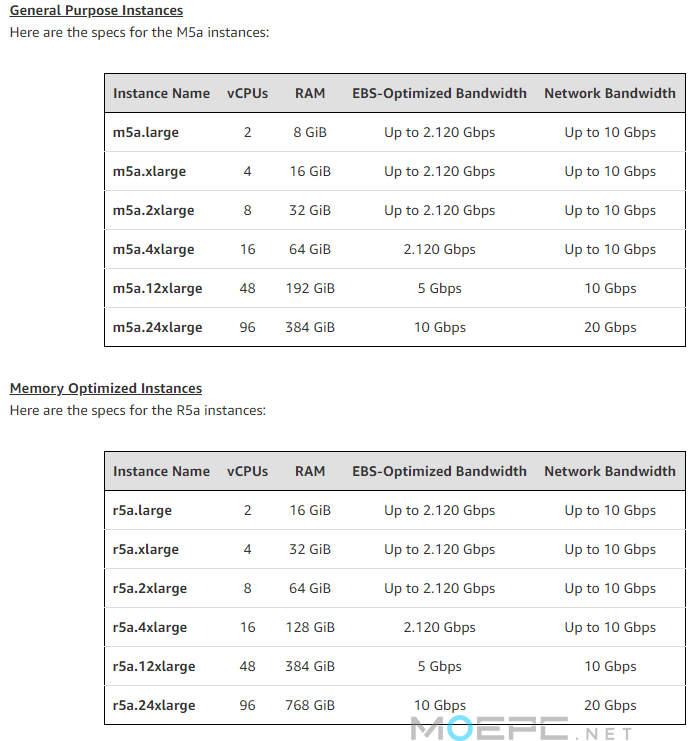

今天起就能使用的有R5a和M5a实例。T3a 需要等一段时间。

R5a,M5a和T3a均采用2.5GHz AMD EPYC处理器,是AMD给AWS的定制型号。

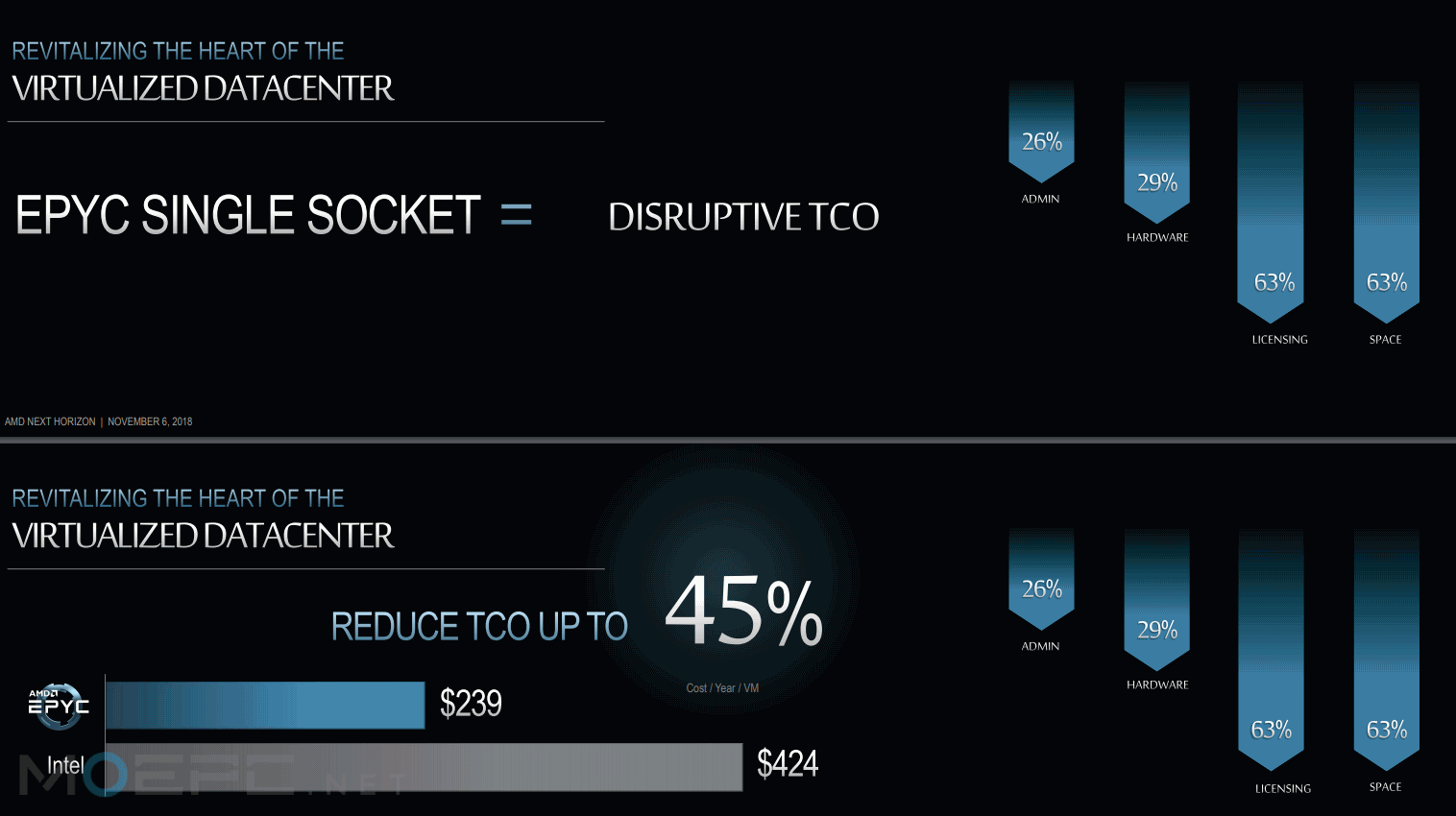

EPYC平台的TCO有很大优势。总体成本更低。

M5a和R5a规格表

目前可以用的有US East (N. Virginia), US East (Ohio), US West (Oregon), Europe (Ireland), 和 Asia Pacific (Singapore) 节点,有按需(On-Demand)、竞价(Spot)和保留(Reserved)实例形式可选。

价格比现有的同等级实例便宜10%。

AMD与CRAY合作打造超算 NERSC-9,“Shasta”将采用Zen3 “Milan” EPYC CPU

AMD还宣布和Cray合作打造新的Shasta超算系统,美国NERSC的下代NERSC-9系统就会用它。

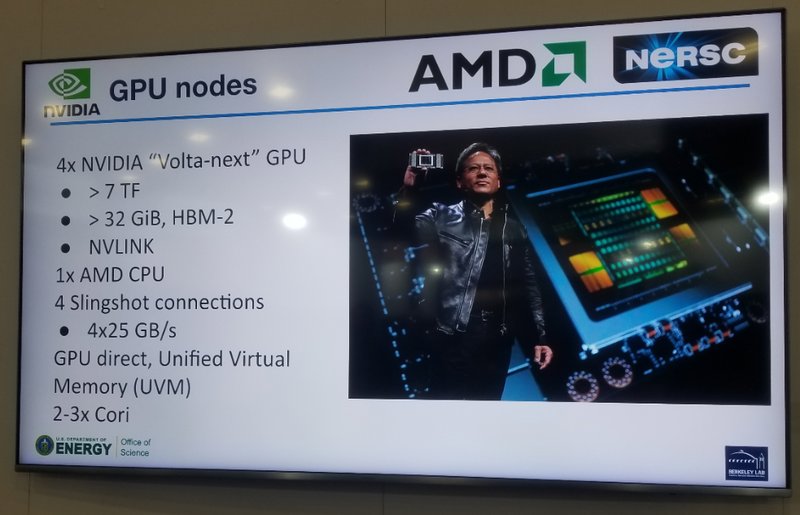

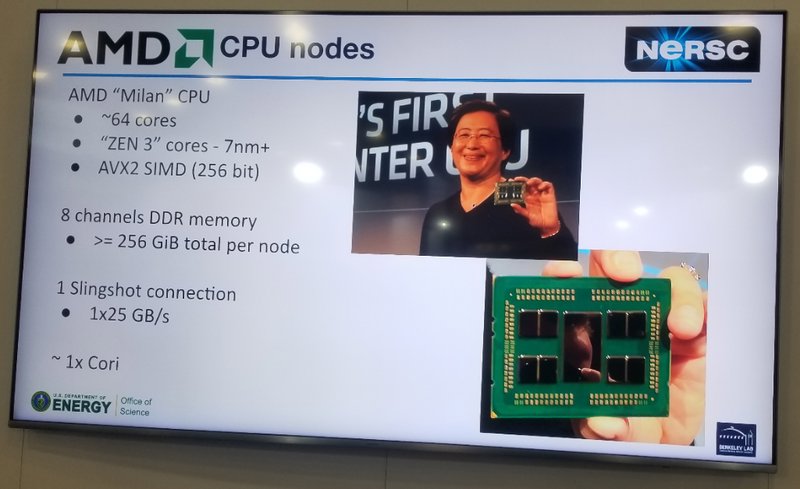

NERSC-9系统代号“Perlmutter”(以诺奖得主Saul Perlmutter命名),采用AMD EPYC + Nvidia GPU,运算能力 100+PFLOPS,预计2020年底交付。

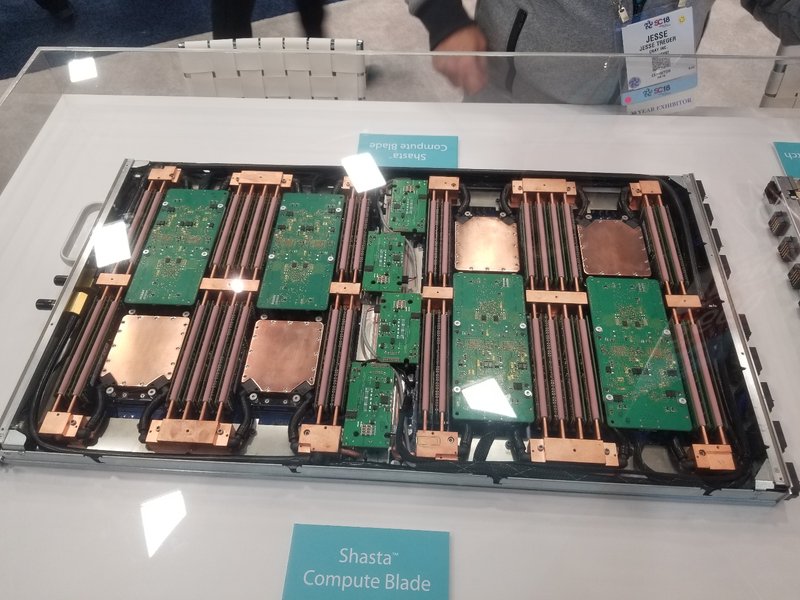

【18/11/14更新:这部分内容来自于SC18大会,作为后续的跟进内容放在这里。

Shasta超算系统将采用AMD Zen 3 EPYC “Milan” + NVIDIA Volta的下代GPU

每个CPU+GPU节点:1x AMD “Milan” + 4x NVIDIA “Volta-next” GPU,4x Cray的Slingshot互联(4x25GB/s),Cori的2-3x性能

纯CPU节点:1x AMD “Milan”,8通道内存,每节点至少256GB,1x Slingshot互联。

文件系统采用纯闪存,也就是没有HDD。

NERSC-9 Perlmutter将提供前代“Cori” 3-4倍性能,功耗>5MW

下代的NERSC-10将会是Exascale级别,预计2024年。

路线图 via:tomshardware

关于”Milan” DOE的发言人没有给出多少信息【目前Zen 3的所有信息都是NDA状态】,只知道是Zen 3架构,7nm+工艺。PPT里放的都还是Rome的规格占位。

Volta下代则是>7 TFLOPS (DP), >32GB HBM2, NVLINK

Milan的核心数、频率、内存规格至少是和Rome同等级,或者高于Rome。

图源:tomshardware

Shasta CPU节点为水冷设计,内置8颗 Zen 3 “Milan” CPU,4个铜制水冷头下面是4个Milan EPYC,剩下的4个则是一样的安装方式,只是方向相反,在绿色的PCB上。

那么问题来了,这里面到底有没有“Milan”的实物。

AMD官方说的是18年下半年“Rome”出样,“Milan” 按计划进行。目前“Milan”应该还处于设计-极早期原型阶段。最近也没有说Milan有流片的消息。

现场展示的这台机子并没有给你看CPU。只看得到水冷模块、PCB和插在里面的内存。

可能性大概就三种,依次递减

- 可能只给你看了台没插CPU的机子

- 可能只给你看了台插了“Rome” CPU和内存的机子 供展示用,而且“Rome”和“Milan”是兼容的

- 真的给你看了有极早期“Milan”工程样品的机子【基本不可能】

NERSC-9是2020年底交付,有充足的时间给Milan。】

除了NERSC-9之外还有个更大的项目。美国能源部的“Coral 2” Exascale 级别超算系统计划很可能会有一台AMD EPYC系统。这个目前还没有公布。

Coral-2项目计划三台Exascale超算,第一台是已经跳了票的Aurora A21超算,是Intel/Cray的。

后面两台是ORNL的“Frontier” 和LLNL的“El Capitan”。Aurora已经跳到了2021年,后面两台只会更晚。

本文地址:http://www.moepc.net/?post=5119

MOEPC.NET整理编辑,转载请保留出处。

EPYC2 图源:computerbase

AMD Zen2 IPC声明:AMD via notebookcheck

Rome 原型主板图:stocktwits

Shasta超算信息:tomshardware

HAWK超算信息:anandtech

Chiplet和IO之间没有硅衬底吗?

@xing0999:说用interposer的都是谣言。

想问下,ZEN和ZEN+是同一个架构吗?ZEN2是新架构?

@Quber:Zen+是Zen的微调 3% IPC

Zen2是全新的。

p30灰烬版都出了

amd就没计划把vega10提提频换个显存再发布一下什么的么

砍掉hbcc 调整核心电压 换2代海力士2gbps满血hbm2

调整下拿出来打2070也行啊

还是说navi有对位2070的小核心

NERSC9采用的是CPU和CPGPU节点并行的方式,按ppt来看纯CPU节点就要贡献1/3的算力,比Summit里IBM的单子肥多了

版主覺得amd的25×20會成真嗎

@VK4502A:25×20 不光是AMD要执行,代工厂的工艺进度也必须跟上

我觉得现在还不用关心2020,先让AMD把2018 2019的承诺兑现了再吧。。

zen1和+还不够成熟的话7nm zen2应该是最好的机会了。现在chrome os可以运行Linux应用了,谷歌也出了界面像样多的x86chrome book,等不及apu有更多移动化应用。

amd太猛了,EYPC的主板不好买,我也用不上,我还是玩线程撕裂者吧。很久没有这么爽过了

@RYZEN:淘宝有售

AMD内部用DKERN + RSA测试,Zen2的IPC为4.53,Zen的IPC为3.5,Zen2在这里比Zen高29.4%

ipc提升29.4%。。。这太可怕

据说下代Zen 3的IO DIE是7nm,还可能用上先进封装

@人类:假消息 文章说了Zen3工艺都没确定

ZEN2 L3缓存是在8核心里,还是i/o die里??

@拉克丝:这个问题挺6哇,在CCX里会造成跨CCX访问延迟,在I/O模块会增加各核心延迟,我觉得更有可能是集成在I/O模块,毕竟集成在CCX中可能会增加IF总线的压力。

@liubeixi:那集成到I/O die L3延迟就增大吧?

@拉克丝:在7nm Chiplet里

不可能在IO Die里。

@拉克丝:建议把我上面写的关于Zen2和EPYC那部分看一遍,我觉得我解释的应该很清楚了。

对于缓存SRAM这种,7nm密度是提升最大的。

L3缓存是Victim Cache

只可能在7nm的CCX里

不然做不到256M这么高容量,放在另一个die上性能也有很大影响。

简单数学:如果用14LPP做256M L3 需要500+mm2面积。

再加上其他的IO IMC

可以轻松达到900+mm2,性能还会更差。

Rome大概率不会在IO Die上集成缓存。

Milan可能吧。只是可能。eDRAM这种做成L4比较合适。

@剧毒术士马文:谢谢纠正,真是班门弄斧哈哈(尷尬)

说起来 AMD这次发布产生 确实是振奋a粉了 微博上那个“无节操的DrBT”三天两头阴阳怪气黑AMD 在发布会前还阴阳怪气的说IOchip是意淫 除非AMD捡到金矿

这会发布会第二天就消失到现在 不晓得是不是自觉没脸见人还是正努力替Intel找AMD毛病

@NiceMing:哦,我关注了他们那一群互相捧场的,分类“人类观察”,乐子不小

@NiceMing:之前微博不少“数码”博主天天碰瓷zen2。。某个装个8700+1060还连发几条微博的,拿A12的提升对比HPC工艺,说啥zen2 4.5G都难,推定zen2 IPC提升顶多3%。还双标A卡,说啥vega56功耗高,买A卡不如不买,转身就只买了个1060,我还以为买的什么2080ti出来上蹿下跳的。转到CPU这块就AMD频率低不适合他,感情AMD得频率比IN高,功耗比IN低,卖的还比IN便宜才瞧得上眼啊

@莫扎特破轮:你说的是mebiuw那货吧

搞了个“数码博主”的v 每天拿七八手的消息乱扯

上次被我戳破了他的弱智言论 恼羞成怒把我拉黑了

@NiceMing:是的,我截了不少图留着明年zen2发布的时候抽脸。不过感觉那货脸皮极度厚,估计没什么用,反正就那一梭子人互相碰瓷

@莫扎特破轮:现在已经开始了

@NiceMing:那个弱智也把我给拉黑了,笑死了

@莫扎特破轮:这么说吧

我最近准备写篇文章

就是一个个揭露这些论坛和微博上的小丑们的。

忍无可忍。

如果你们都有截图的话可以发我

没有的话可以先截图存档。

@剧毒术士马文:好的。整理了大概17张图片,主要是造谣,无脑黑,意淫类的

@莫扎特破轮:看到了

@剧毒术士马文:人要脸,树要皮,今天某博主又开始不要脸的黑起了zen2构架。。

@NiceMing:哈哈哈 果然是昴着劲憋文呢

扬言自己出差好几天

前几天说这个架构是“意淫” ,他的“意淫”潜藏的含义是什么?AMD没能力做到。

今天憋出来的狗屎就变成iochip是北桥复辟的垃圾

@NiceMing:而且我就猜到他肯定要通过扯mi60来变着法黑AMD

@NiceMing:哈哈,看到了,在选择性发MI60和V100的对比图指点,可惜他也就买得起1060

@莫扎特破轮:啧,我也看见了,果不其然还是主观第三方、mebiuw那几个,想打他脸有点太简单了

@NiceMing:第三方那个啥的,最近收敛了点,不过还是脸皮厚的在黑zen2,说什么要是zen2真那么厉害绝对价格比友商的9900K高,他怕是不知道奔腾4是怎么又烂还卖的又贵的。就剩最弱的那个一直在跳,变着法的黑

@NiceMing:那几位大概是heip AMD上瘾了罢

发布会吹了一段自动驾驶呢

@5256qpqp1:那个是演示MI60的深度学习性能的

@剧毒术士马文:好像是跟叫HIGHWAI公司合作的?

网上找不到???我感觉就是做自动驾驶的创业公司?

@5256qpqp1:就是个DEMO而已。。展示深度学习和模拟能力的

名字叫highwai CEO Peter McGuiness

这种的一般只会在DEMO上出现一次

然后就再也没有消息

这方面目前还是NVIDIA的主场。无论是硬件还是软件

@剧毒术士马文:自动驾驶实现上是Intel旗下mobileye的主场吧,NV这块大饼到现在还没成

想了想要这个硬件虚拟化 总觉得也许可以是未来的网吧解决方案?

没有L4并且L3都在CPU die上的话缓存一致性要求会很高吧(

强,无敌!

马文居然诈尸了

现在我更加坚信农企临时工是一份比较好做的工作了,各种意味上的。

另外颇具讽刺意味的是我拱火失败,要去CHH避难了。

@轮子妈:看不懂什么意思

@Hindy:问就是恰饭,虽然我非常厌恶这个梗

或许可以像超ring一样超if了

64核/56核 =1.14

但是,单路64核比inte双路组成56核仅快10% ,性能看起来没强多少。

是因为zen2 rome 64核主频率远低于 双路56核频率 ?

@超频养成方法:双路8180M 410W,单路epyc2还是非量产版,已经不错了

@超频养成方法:8180m 非avx应用全核3.2的频率,epyc64c估计很难达到这个频率吧(这个benchmark好像刚好没用到avx)

@FlyWood:用的是AVX2。

@剧毒术士马文:256M L3的说法是哪来的呢?没有看到官方说啊

@FlyWood:官方现在没告诉你罢了。等到放出架构进一步细节的时候会说的。这又不是像以前做翻译一样直接翻译,这是我自己写的文章。

如果对比一下的话会看到写的很多都是anandtech还没有的东西。

@FlyWood:8180M这个数据没几个大客户会用的,巨头的data center几乎都是定制版CPU,想要什么性能随意改

@超频养成方法:单路打双路,OK?

比起单路8180M算强了一倍多。

8180M俩的功耗能有410W TDP,Rome的TDP大概只有180-250W。

Intel未来的单路CLX-AP都不会比双路8180M强。

CLX-AP还是新插槽,新平台,需要水冷。

TCO比Rome高得多。

Rome还有双路系统,向后兼容目前Naples。

这只是为了展示Zen2在功耗和性能上的巨大优势。

文章里说了Rome 是未超频风冷频率未定的原型版。最终版的频率会高一些。

@剧毒术士马文:马文,是不是现在除了7nm,amd的显卡和cpu还都是gf负责生产?

@amdfans:目前AMD的14和12都只有GF做

@超频养成方法:在推上亲自问了Charlie Demerjian,说Rome目前是测试芯片,最终频率还能提升10%上下。而且Rome 205W的TDP,对比Intel双路410W的TDP

理想情况下ipc提升30%,同功耗下频率25%

@23333:最理想的情况下

IPC对比zen1代提升30%。。真的假的,要是真的话9900K液氮6G单核都虐杀

AMD真会玩,胶水玩的真6

希望主流AM4平台能有12核

I/O die很有可能集成了L4 cache,不然64核心的巨大吞吐量仅靠L3不一定满足。CSL-AP即使出8180M胶水也无卵用了,7nm面前就是弟弟。更别提有些大佬定制的300w TDP Roma。不过显卡部分有好有坏,好消息是在晶体管没涨太多的情况下实现1/2 双精度(终于阉割了the king无用的电阻丝),坏消息是7nm Vega架构比老黄12FFN能耗比还不能占优,这边的节奏要落后18个月(CPU节奏正好超前18个月),明年navi大核心才有可能把节奏缩小到12个月

@在amd看大门:按照马文所说L3已经256MB的话,io die里面应该不可能再塞一个更大的L4了吧。

@LV3的萝莉控:yep,确实没设置L4

@在amd看大门:IO DIE尺寸上可以集成缓存,但目前还没确定

@在amd看大门:有L4的是twitter上某退休工程师设想的架构

然后被某些人盗图到某论坛。

我在anadtech的live blog里没有看见L3翻倍的说法?也没在ppt上看见关于L3的信息啊?

4.0×1.25

4.25/4.3×1.25

哪个对呢?

@wangbaisen1990:不过统一的iocore出现以后

分各种ccx的意义,已经不大了吧

Zen 2 支持 256-bit AVX2 运算,仍然使用 MCM 多芯片设计,但采用了与第一代不同的方法,它将内存控制器、Infinity Fabric 端口、PCIe 通道剥离出来,集成一块 14 纳米的 I/O DIE 上,与 7 纳米的 CPU 封装在一起,新的设计解决了第一代的内存延迟问题。

zen2 一个8核die 由2CCX组成? 不是 1CCX=8核?

@超频养成方法:这个我也很好奇!难道Zen 2不是1x8C CCX吗?

消費級開for am4的io die好處是ccx die可以延用台積不用開新的光罩

io die用14nm除了良率成本以外io電路用7nm效益不大

而且io die裡不少東西是買別人IP塞進去的電路無法優化

@望月:同样CCX Die的话AM4就必须集成个更小的IO die,面积切成四分之一

@剧毒术士马文:如果跟前代一樣2ch+24lanes應該能砍不少

雖然pcie3.0改4.0也佔不少面積不過我覺得還行

Zen2的核心布局优化得太好了,居然将IO独立出来平衡了各核心的延迟。

有点好奇的是,服务器和High-End平台可以用这种布局优化,但对消费级来说是没什么卵用的吧?那么消费级的提升可能没有服务器和High-End提升那么大?

@liubeixi:消费级大概是见不到了……

1. 有些疑问, PPT里有提到7nm同功耗下性能提升25%, 这个25%是指单纯的频率提升,不是指CPU性能提升吧? 比如的ZEN+全核3.7g 100w左右, 当 zen 2 100w 频率可以达到3.7*1.25=4.62G ?

2. zen2 桌面处理器会是什么样的形态。 是1dei 8核(1ccx) + 1/O die ? i/o 独立后对内存超频、兼容、延迟有什么影响? ZEN2是不是小白用户随手也能上3600 4000内存频率?

@超频养成方法:工艺上 性能基本=频率

另外EPYC应该是2CCX。两个4核CCX

I/O die是EPYC解决延迟需要的。桌面并没有集成I/O die的必要

请问北桥还是独立的时候影响过兼容性吗

@剧毒术士马文:桌面不集成IO芯片的话,那IO咋办,核心die已经没有IO模块了吧?

为什么io die不用7nm呢

@LV3的萝莉控:成本 良率

14nm的IO die很大很大。至少有250mm2+

@剧毒术士马文:IO die这么大,桌面级会不会因为成本而不使用IO die?

还有一个核心die里面到底是1个8核CCX,还是2个4核CCX?

@LV3的萝莉控:第二个问题已经知道了,刚刚看到你文章有说。。。

停一下,SP3是4094吧,上面是不是打错了

@potato:已修正

ROCm的负责人在几天前跳槽牙膏了

@NiceMing:这个老新闻了。。

@剧毒术士马文:就前几天推特自己说的嘛 Reddit吵翻天

多核狂魔AMD放大招了啦!

弱弱地问一句:IMC是否改进了?DRAM延迟高是否改善了?

AMD, yes!Intel, 吔屎!

以后zen2桌面消费级就是单die8核了吗

@parker:本来Zen就是单die八核,没有变化。

@剧毒术士马文:有没有单CCX8核的消息?

还是说在ZEN2上已经不需要CCX的概念了?

@luluehh:No :)

@luluehh:会上有人问了。

AMD的代表说没法透露更多架构细节。

如果有新消息会第一时间更新。

马文码文速度第一!