3D NAND微缩极限近了吗?

在今年的闪存峰会(Flash Memory Summit)上,三星(Samsung)宣布开发1Tb 3D NAND,并将用于明年推出的商用产品中。不过,我想知道4Tb 3D NAND何时将会出现在市场上。

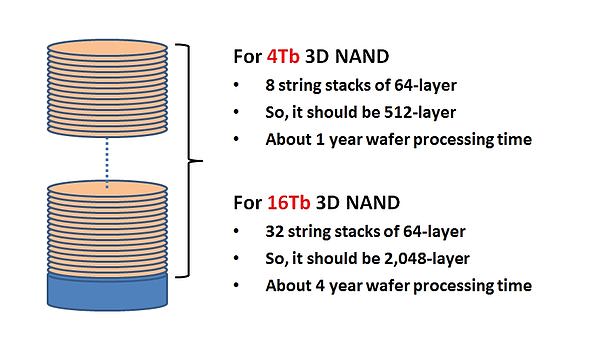

根据来自三星与东芝(Toshiba)的资讯,64层TLC 512Gb 3D NAND晶片尺寸约为130mm 2。而假设以串列堆叠64层的条件下,我认为,为了建置4Tb NAND晶片:

1.需要8串64层串列堆叠,才能实现容量达4Gb的晶片(512Gb×8=4G);

2.总层数在130mm2的晶片尺寸上达到512层;

3.处理1个晶片大约需要1年的时间,闪存逻辑则需要5周的处理时间;再将建置一个64层闪存单元需的5-6周时间乘以8倍(8串64层的堆叠)。因此,处理一个512层的晶片将会需要45-53周的时间。

如果这种简单的估算方法正确的话,那么实际上就不可能实现4Tb NAND晶片了。如果考虑采用4bit单元(QLC)以取代3bit单元(TLC),那么充其量最多也只能改善25%。因此,QLC 4Tb 3D NAND需要410层,以及大约9个月的晶圆处理时间。

那么16Tb 3D NAND呢?它应该会需要2,048层,以及大约4年的晶圆处理时间。

过去几十年来,NAND在摩尔定律(Moore’s Law)的原则下实现了显著的成长。当摩尔定律逐渐迈向尾声,而平面NAND开始过渡至3D NAND时,许多人预期3D NAND将以垂直方向持续扩展其存储微缩。然而,3D NAND在64层时才能实现与平面NAND相当的价格。因此,3D NAND将开始与平面NAND展开价格竞争。而现在我认为期待4Tb NAND几乎是不可能的。

3D NAND的微缩极限似乎也变得显而易见了。那么,3D NAND将会很快地达到其生命周期的终点吗?我想可能不远了。

编译:Susan Hong

(参考原文:Limitations of 3D NAND Scaling,by Sang-Yun Lee, CEO, BeSang Inc.)

via:https://www.eettaiwan.com/news/article/20171011NT01-Limitations-of-3D-NAND-Scaling

AMD的融合硬盘技术很不错,也许未来并不需要太大的SSD。