3个原子厚度芯片原型诞生,二硫化钼将重新推动摩尔定律

二硫化钼,这个超薄金属、硫化物,拥有令人惊叹的电子特性,或将成为石墨烯有力的挑战者。

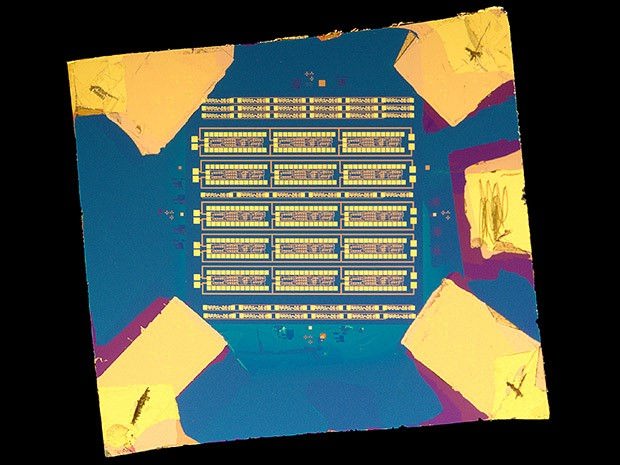

在摩尔定律在使用硅遇到无法逾越的障碍时,科学家们希望能通过二维材料,如石墨烯或二硫化钼等来帮助摩尔定律继续快速发展。现在,科学家们利用二硫化钼制作的原型处理器消耗大约60毫瓦,包含115个晶体管。它的设计者希望还能集成更多。

维也纳大学(VUT)的研究人员开发的3个原子厚度的芯片,可能是第一个二维材料的实例。

以前,由二维材料制造的芯片,上面集成的晶体管数量保持在个位数,而VUT大学的Thomas Müller和他的同事创造性的达到了115个晶体管。他们将其成果发布在了4月11日《自然》杂志上。

该微型芯片可以执行用户定义的、存储在外部存储器中程序,执行逻辑操作,并将数据传送给外设。虽然这个原型运行在single-bit的数据,但研究人员说他们的设计很容易用于multibit数据。

他们还指出他们的发明是兼容现有的半导体制造工艺。

该芯片由二硫化钼的薄膜制成,类似于一层钼原子夹在两层硫原子之间。这个薄膜只有0.6纳米厚。相比之下,硅芯片层的厚度约100纳米。

“这是令人兴奋的,发明者,就已经能够使用一个只研究了5年的、原子厚度的二维材料制造出如此复杂的电路,”Eric Pop说。Pop是斯坦福大学的一个电气工程师,他没有参加这项研究。

那么,二硫化钼的摩尔定律是什么呢?

VUT的原型产品最小尺寸是2微米。然而,Müller说:“做到200纳米或100纳米晶体管的管道长度应该是相当简单的。”

他补充说,随着这些电路中电触点的质量改善,最终应该能做出1纳米的二维晶体管。Müller说:“这个数字用硅是没法实现,硅的极限应该是5纳米。”

最大的障碍是良率

用二硫化钼制造更复杂的微型芯片,其主要障碍是制造。目前,Müller团队的全功能芯片的良率只有百分之几。

提高晶体管良率的一种方法是培育更均匀的二硫化钼薄膜。不幸的是,当它们从蓝宝石基板上转移到它们的目标晶圆上时,它们的缺陷就会出现。

研究人员目前正在研究如何在目标晶圆上直接种植二硫化钼薄膜,以免除“转移”这个步骤。 通过提高二硫化钼的均匀性,“将二维电路的复杂性增加到成千上万的晶体管,应该是相当简单的。”

用于原型器件的目标晶圆是硅,但研究人员说,理论上说其能在几乎任何基底上生产。

“如果电路能在柔性基板上演示,实现硅电路不能做某一个独特的功能,那将是一个重要的未来发展方向。”斯坦福大学的Pop说。

但是,如果二维微处理器能像现代硅芯片那样集成数亿个晶体管,那么另一个重要的改变是必要的。Müller说,工程师们将不得不从这个原型中使用的n型晶体管设计,转变为在传统芯片中使用的低功率的CMOS设计。

“这可能需要另一种二维半导体材料来替代二硫化钼,我们有足够的选择,如二硒化钨。”他说。

迈向下一代电子器件的初始阶段

“至于性能、原型电路的总能耗约60毫瓦,它运行频率为2至20赫兹,”VUT研究人员表示,“我们的器件当然绝不与目前的硅基微处理器竞争。这只是迈向新一代的电子器件的初始。” 斯坦福大学的Pop同意上述观点。VUT的芯片的场效应电子迁移率(电子流过晶体管的容易程度)相比其他二硫化钼薄膜“至少比现有水平的差一个数量级。”他解释说。

二硫化钼的电子迁移率大约是100cm2/vs,即每平方厘米每伏秒通过100个电子,比非晶硅和其他超薄半导体的迁移速度更好,能制作出更小的晶体管,这意味着在同样体积的芯片上就能集成更多晶体管。

低迁移率的二硫化钼电路将运行且效率低下,但我们的迁移率将会得到改善,Pop指出。

本文部分内容翻译自IEEE Spectrum

via:http://www.ednchina.com/news/article/20170602VUT