技术互补DSA加EUV实现精细间距光刻

DSA于21世纪初得到初步发展,并在随后几年里引起了主要半导体制造商的高度关注,后来在一定程度上失宠,部分原因是EUV光刻获得了重要投资,取得了进步。然而,DSA材料及工艺的最新进展,可望打消延迟实现的疑虑。

选择合适的光刻技术,不一定要非此即彼,二中选一。结合使用EUV光刻及DSA技术,可能会创造难能可贵的机会。虽然两者有时被看作是竞争对手,但将其视为相得益彰的互补型技术,则更加合情合理。本文介绍了结合使用EUV和DSA技术为光刻技术带来的益处,以及此前存在的障碍变得无足轻重的原因。

材料定义图案

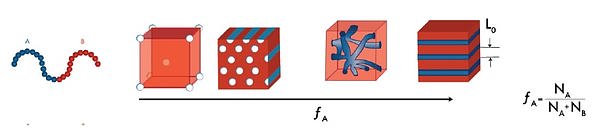

大多数光刻技术采用掩模定义图案,然而在DSA工艺中,图案存在于材料本身,这就是它与众不同的地方。用于DSA的原始嵌段共聚物(BCP)结合了聚苯乙烯(PS)和聚(甲基丙烯酸甲酯)(PMMA)。这两种聚合物能自然而然地将自身分离成独立相。调整PS-b-PMMA材料中的PS及PMMA的相对比例,使形态由球形变为圆柱形,再变为层状形态(图1)。Flory相互作用参数χ及片段长度的乘积,决定了有序结构的间距。χ值越大,所得结构的间距越精细。

图1:BCP类形态作为组分的函数。当Α组分的占比增加时,结构从球体变为圆柱体,再变为层状。图中L0指特征域长度尺度、N为链段数。

标准PS-b-PMMA材料具有相对较低的χ,将间距限制在20nm或更大。一些材料制造商正考虑使用PS-b-PMMA以外的化学成分,生产高的BCP,用聚二甲基硅氧烷或聚羟基苯乙烯代替PMMA组分。更改PS-b-PMMA亦可增加χ,亦可能调节χ、分子量及玻璃化转变温度,在各种退火条件下,实现14nm~40nm之间的层片间距。

BCP沉积的工艺比较简单。旋涂在基材上的中性层,可使BCP在热退火过程中分离成单个域。中性层不对BCP中任一聚合物链具有亲和力,可使域分离。聚合物域分离负责图案形成。

工艺注意事项

DSA沉积过程使用此两种基本方法中的一种。制图利用地形学对准BCP,沉积在相对较深的沟槽中。引导图案决定沟槽,将BCP限制在其优先方向对准的图案。化学外延法基于平面基底上的化学图案,其上是BCP自对准。

半导体产业正追求制图外延结合化学外延,有利于制图外延法产生细间距穿孔,亦有助于化学外延创建并行线数组。

退火温度在250℃~275℃之间,符合标准半导体工艺规范。退火过程可长达两个小时,使所创建结构的缺陷率足够低,但增加了工艺成本。

PS-b-PMMA BCP正在大规模量产。目前,全球有110万吨此种材料用于各种应用,如此庞大之数量,超过了整个半导体产业的需求。因此,未进行商业化生产的DSA材料当前目标为满足半导体应用,但产业准备就绪之时,且已安装基础设施,便可扩大适合材料的生产。

DSA正红的原因

2007年DSA入选国际半导体技术蓝图(ITRS)。起初,主要半导体产业企业认为,DSA会在14nm和7nm之间的任一逻辑节点迈入商业生产,甚至动态随机存取内存(DRAM)可以更快地实现商业生产;但目前为止未能实现。2016年DSA研讨会调查显示,DSA技术尚不具备成为主流技术之条件,且在未来数年内也不会成为主流,但是一些整合零件制造商想推进DSA工艺发展,也有支持此举不仅具备可能性,也十分可取的理由。

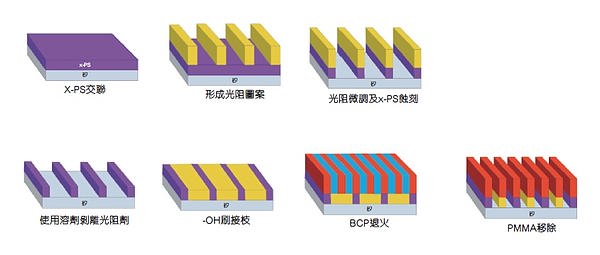

图2:使用含硅抗反射涂层(Si-HM)的色调反转制图外延法(TIGER)的示例工艺,包括光刻、DSA沉积及蚀刻。

将波长降低到193nm浸润式光刻,使线宽和间距降至80nm。自对准四重图案化(SAQP)等技术,可以透过多次光刻/蚀刻迭代产生更小的特征,惟需添加光刻步骤,每一个都需要定制掩模。

浸润式光刻技术快走至穷途末路,亦为下一代光刻技术提供了机会。在10nm~30nm关键尺寸(CD)的设计,为此等最先进的技术创造了最佳条件。

EUV光刻技术的进步,为业界青睐DSA的一个因素。当今的EUV材料与老一代产品相比,具有更高的灵敏度,因此需要较低的紫外线剂量;线粗糙度亦有所提高。EUV光刻可以产生30nm或40nm间距的通孔,但浸润式光刻无法做到。

DSA的较高分辨率,甚至超过了半导体产业当前需求。当前,特征尺寸发展水平,可使DSA尤为有效。若此趋势继续发展,到2020年末,人们会广泛使用此技术。

DSA及EUV两相结合相得益彰?

最有效的解决方案在于综合运用EUV和DSA技术,将每种技术的优点发挥到极致。这两种方式都能让分辨率达到与N7和N5逻辑节点兼容的水平。EUV光刻工艺非常适合多种不同间距的曝光设计,这些间距低至线宽,并且间隔大约为30nm。然而,对于此类精细间距,需要的光罩步骤数量可能会使这项技术非常昂贵。尤其是在高产能率下,局域线宽均匀性(LCDU)也是一个很大的问题。

最初的硬质光罩光刻工艺对于EUV和DSA是一样的,但它们在曝光过程中有差异。一旦BCP沉积,DSA无需额外光罩即可达到30nm特征尺寸。退火自然地将这两个阶段分成不同的形态,但是DSA工艺最适合单一间距的设计。

EUV可用于在晶圆上绘制分辨率较低的特征,并制作后续DSA沉积的间隔物。这种组合提供设计最大弹性的同时,又简化了制造过程,达到消除工艺步骤和减少光罩成本的目的。与单一的EUV相比,LCDU更好一些。

DSA最适合具有多重、重复、普通精细间距特征的装置。因此,它可能会首先被用于DRAM中,随后会用于逻辑设备上的层中。尤其是利用EUV来沉积间隔物时,使用DSA制图能实现更复杂的设计,满足不同地区对芯片间距的不同要求。这大概是选择芯片的方法。

图3:DSA材料化学外延法 Liu-Nealey(LiNe)工艺工艺。

尽管有运用DSA和EUV的承诺,只有供货商能说服整合设备制造商(IDM),让他们相信这种材料已经克服了技术限制,半导体产业才会转而使用这种方法。DSA遭受了很多挑战,导致它被推迟采用:基本的问题包括缺陷、曝光放置准确度、整合至制造工艺的难易度和成本。但我们有理由积极看待这些问题,随着化学的进步,就这些度量标准而言,工艺方法上都有了提升。

克服技术挑战

2016年的DSA研讨会调查中将缺陷确定为最大的技术挑战。缺陷和成本是相关的,因为最低的缺陷等级往往伴随着最长的退火时间。使这两个阶段分离只需低至5分钟的退火时间,但最后的材料含有太多缺陷,导致其不适于商业使用。

每次只能给一片晶圆退火,这使退火成本大幅提高。然而,最近的研究显示,立式炉中运用批量退火可望能大幅减少成本,透过给150个并行的晶圆退火30分钟,研究者能充分论证透过比SAQP更低的成本达到低的缺陷等级。

同时运用DSA和EUV将有望缓解曝光放置错误的问题。例如,EUV光刻工艺能为双峰穿孔制造自组装孔。在EUV过程中,这两个穿孔可能会合并,但在DSA过程中又会自动分离。在没有DSA的情况下,为避免合并的穿孔,可能需要额外的光刻工艺步骤。

当穿孔形状优化时,对于精细间距的穿孔,运用EUV和DSA的方法最可靠。研究表明,花生形状而非椭圆形,最适合以最低风险的曝光放置错误来制造自组装穿孔,甚至对于最具挑战性的N5节点也一样。

合作以加快DSA采用

半导体产业在光刻工艺方面有大量的经验,但DSA需要我们在思维模式上做出转变。BCP材料在半导体产业内还是新生事物,它在材料上的改变是革命性的而非渐进的,因此这一过程可能面临诸多阻碍。在将DSA材料投放到半导体市场交易之前,需要在实际装置上示范使用这些材料。

为填补这一空白,需要半导体产业材料供货商和在BCP方面有资深经验的化工公司的鼎力合作。这样的合作已经在进行中了。Brewer Science已经与Arkema合作,后者是一家有20几年生产BCP经验的公司,但几乎从未涉足半导体产业。两家公司的合作关系确立于2015年,开始了DSA材料的试产,这为这项技术从实验室到运用至商业半导体产品的过程铺平了道路。

DSA和EUV应该被视为相辅相成而非互相竞争的技术,它们最终会成为精细间距光刻工艺运用在N7等节点的主流技术。业内企业应跳出孤军奋战的局面,且材料供货商和化工公司应建立合作关系以迎接这种转变。

作者:Douglas J.Gerrero,Brewer Science,高级技术专家暨比利时微电子研究中心(IMEC)成员

via:eettaiwan