数码科技

富士通公布自研深度学习处理器细节

http://www.moepc.net/?post=2482

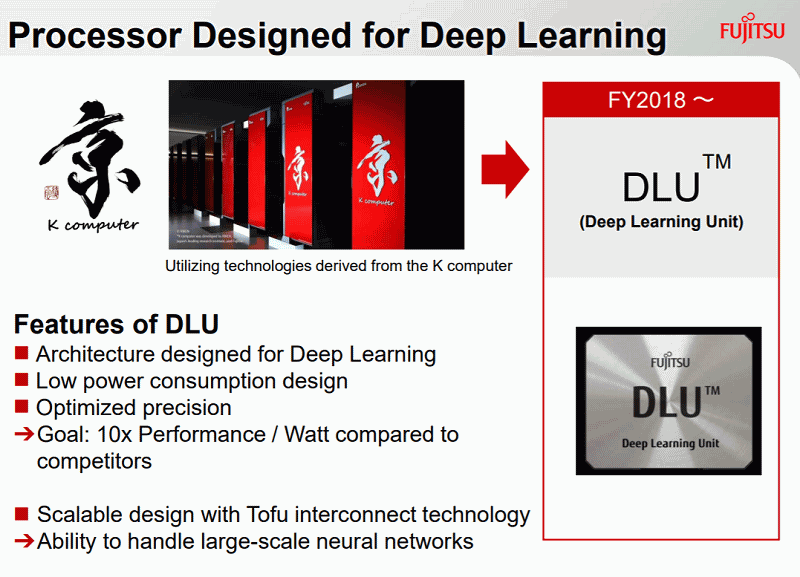

富士通开发的AI处理器称为深度学习单元(DLU)。富士通的设计目标是比对手高出10倍的每瓦特性能。

DLU至少在2015年开始研发,富士通没有透露过太多细节。上个月的ISC2017上富士通AI平台部门的高级主管Takumi Maruyama提供了更多信息,他自从1993年就参与SPARC的研发,目前正参与DLU计划。

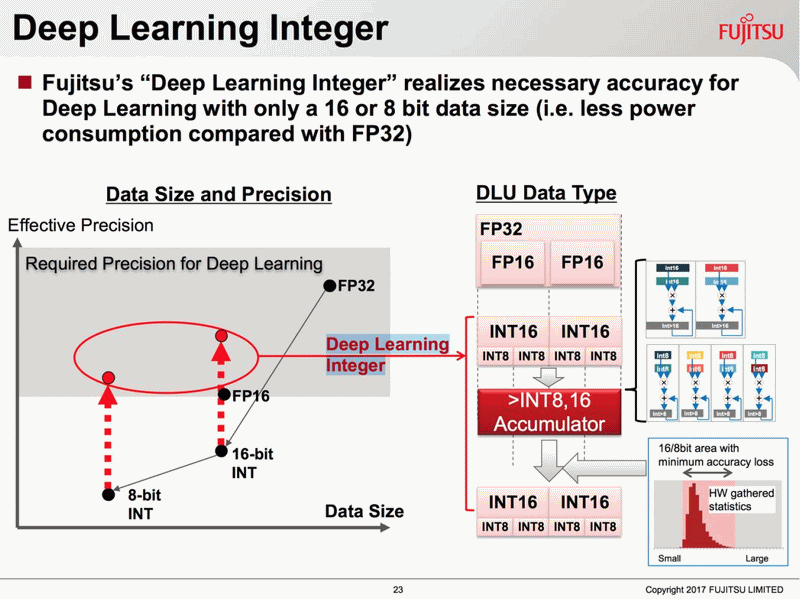

DLU倚赖低精度计算来最佳化深度学习的性能和能效。DLU原生支持FP32、FP16及INT8。

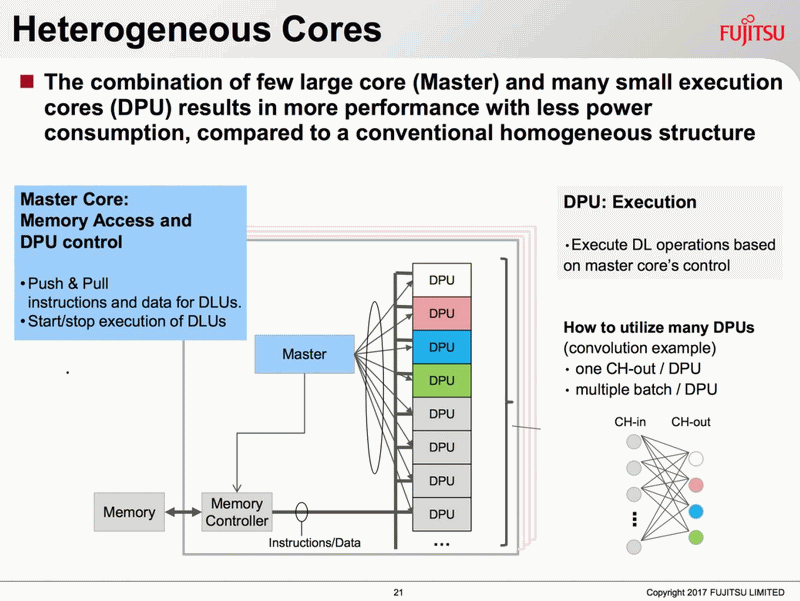

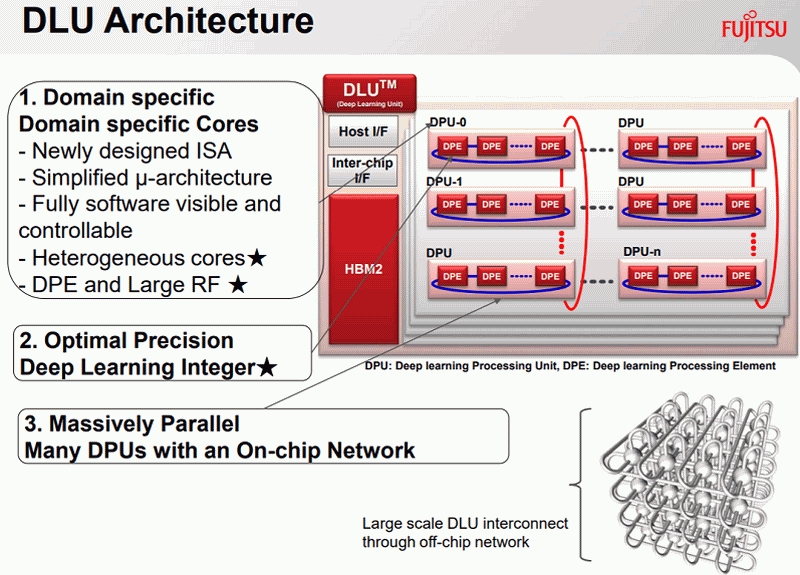

DLU芯片包含数颗DPU,DPU间使用高性能互连。有独立的主核负责管理DPU的执行,协调DPU间以及DPU到内存的访问。DLU芯片将会集成HBM2,DLU与DLU间使用Tofu互连。

DPU由16个DPE(深度学习处理单元)构成,每个DPE包含8个为深度学习定制的SIMD执行单元,以及一个很大的寄存器堆(RF)。与缓存不同,寄存器堆受软件的完全控制。

在2018财年,首代DLU将作为一颗协处理器问世,需要主处理器来驱动。从第二代开始,富士通计划将DPU集成进主处理器,时间未知。

http://www.moepc.net/?post=2482

via:https://www.top500.org/news/fujitsu-will-pursue-ai-with-custom-built-processor/

MOEPC.NET编译,转载请保留出处。