【Anandtech】GlobalFoundries 7nm详细计划: 三代工艺, 700 mm2, 2018年大批量生产

本文地址:http://www.moepc.net/?post=2308

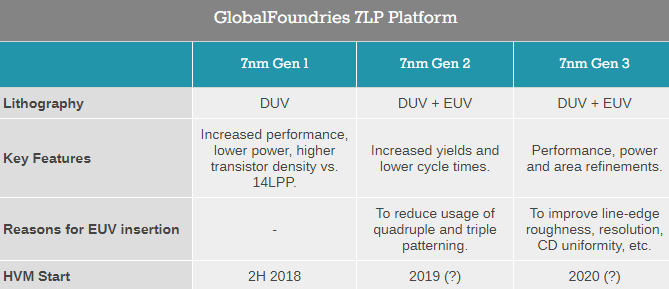

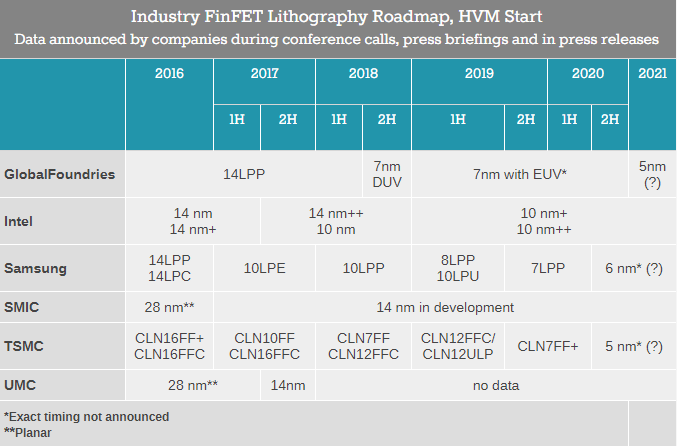

最近GF提供了关于7nm工艺的更多细节。GF在7nm FinFET上将有多代工艺,包括EUV。

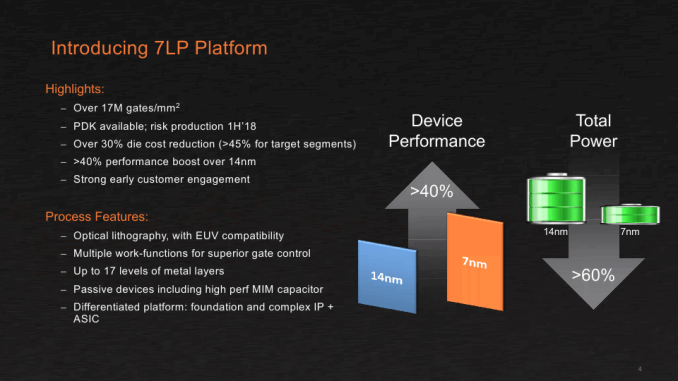

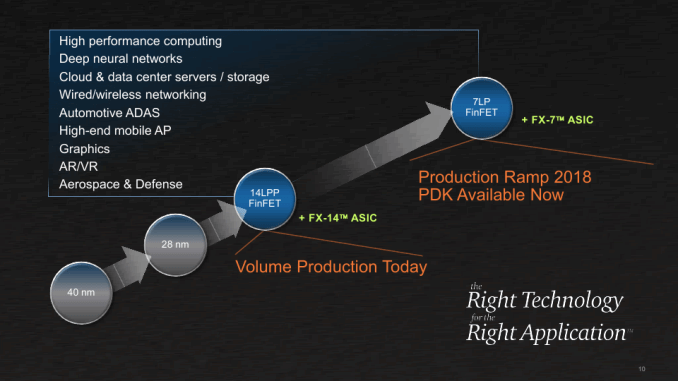

GF的7LP(7nm Leading Performance,不是低功耗)将有3代,芯片面积最大700mm2。采用7LP工艺的首款芯片将在2018年下半年大量生产。

7nm DUV

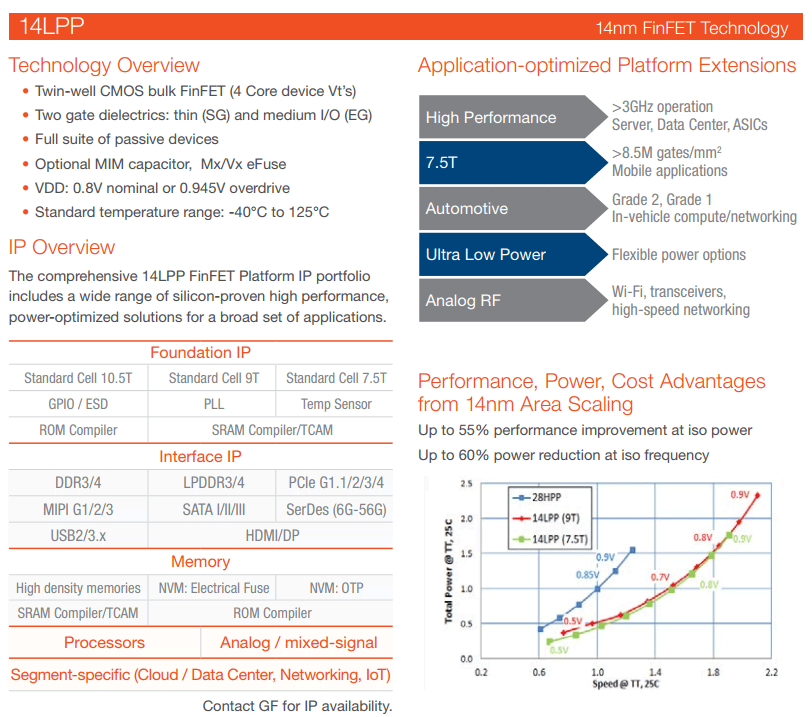

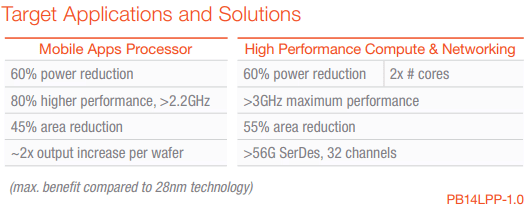

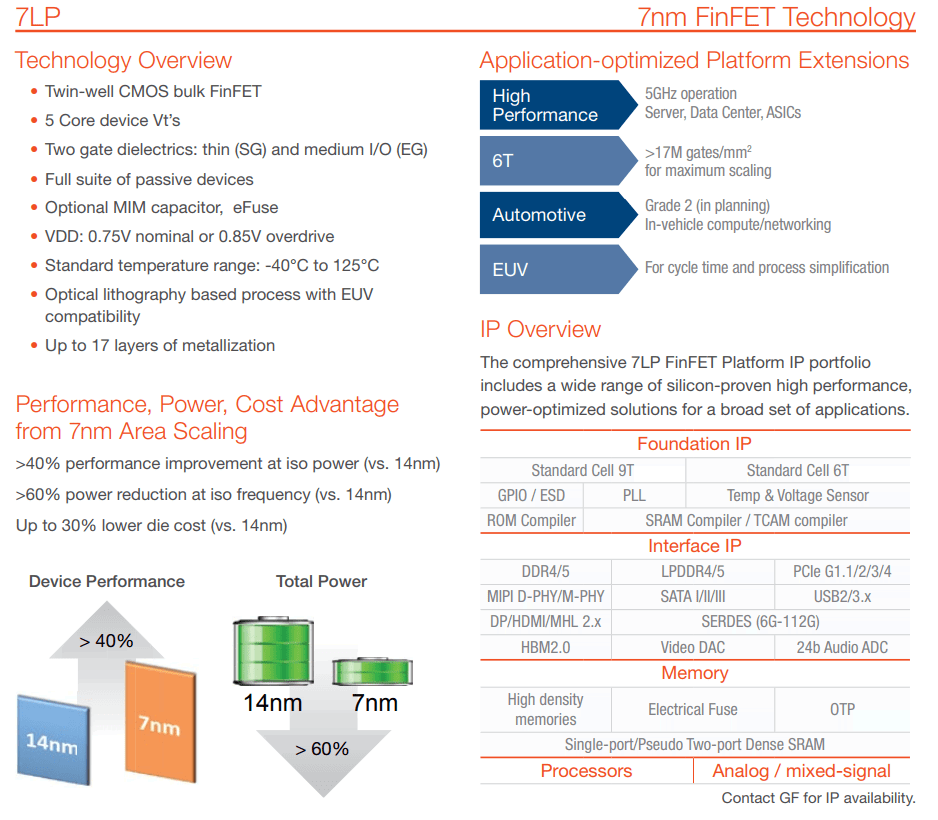

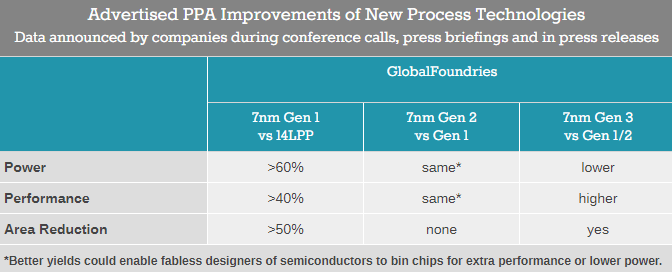

最先登场的第一代7nm工艺采用DUV深紫外光刻,搭配氟化氩准分子激光(波长193nm)。GF的7nm目标之一是同样功耗下较14LPP提升40%的频率潜力。同频率则降低60%功耗。

14LPP频率目标为>3GHz

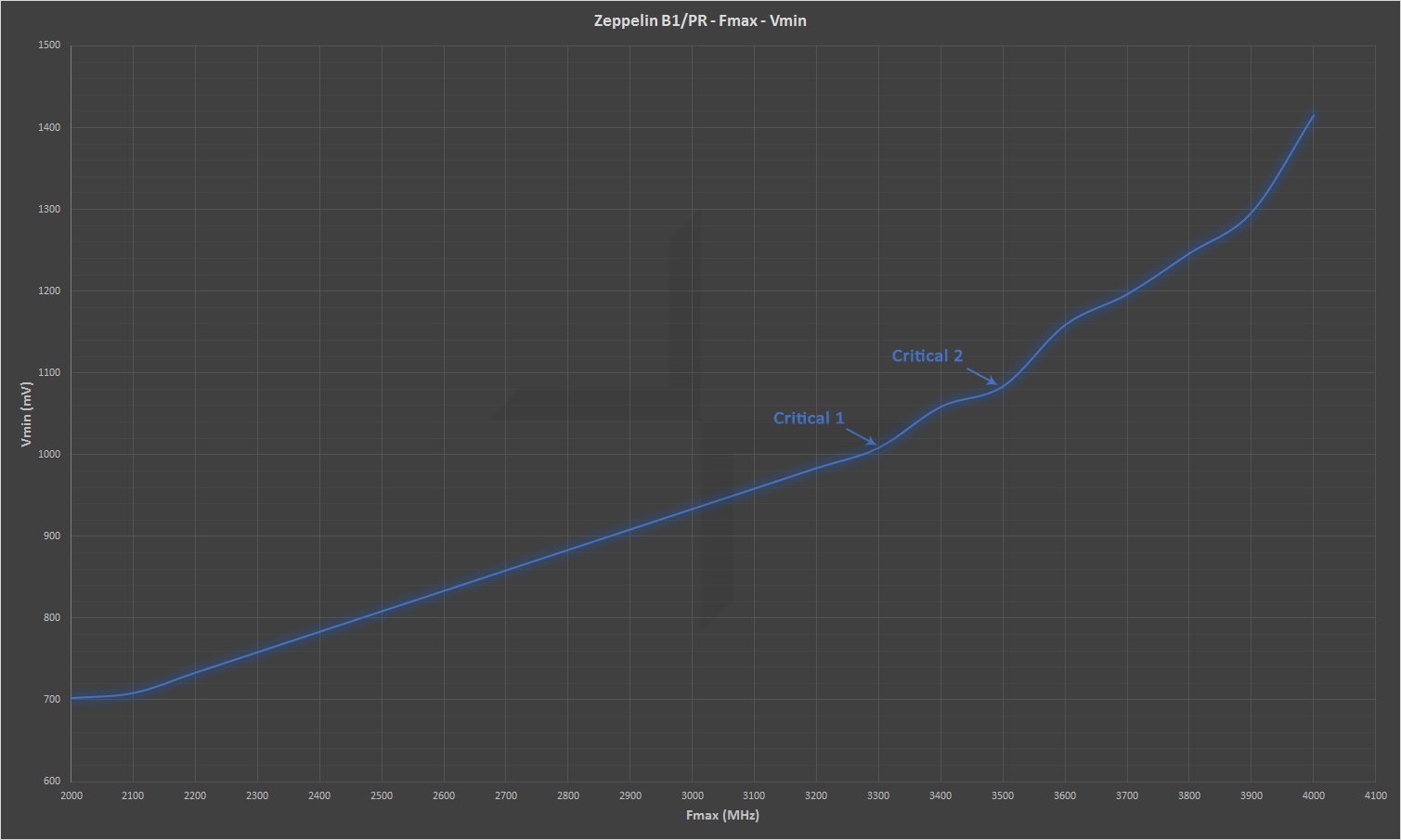

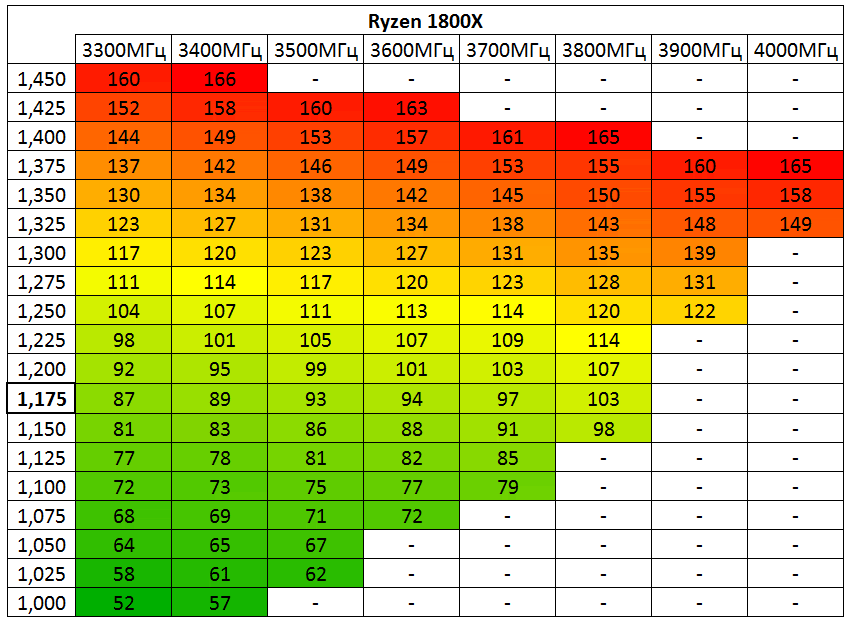

Ryzen的14nm LPP在3.8GHz之后电压需求猛增

而7LP制程的频率更高,为5GHz – 实际频率表现应该比14LPP要好。

7LP工艺将支持0.65-1V的低电压,同时将带来更好的门控。

成本和大小方面,7LP与往的制程提升稍有不同。一方面,7nm DUV的尺寸比14LPP缩小50%以上,由于14LPP使用的是20nm BEOL互连,有这提升实属正常。然而7nm DUV将有更多层,需要三重或四重图案化,所以实际的成本降低大概在30-45%,取决于应用场景。

取名为7LP,Leading Performance的原因是这代工艺的主要目标将是高性能,而不仅仅是手机里的低功耗SOC – 和台积电7nm相反。

GF计划使用7LP生产多种芯片,包括高性能CPU,GPU,移动SOC,国防、航空用芯片,以及汽车领域的应用。

7LP提供更好的晶体管密度(主流设计下每平方毫米1700万晶体管)和频率潜力,同时将最大芯片面积从14LPP的650mm2提升到约700mm2。

前几个季度里,GF已经在给客户试产7nm晶圆了。7nm DUV制程的芯片都在设计中,预计GF会在2018年初风险试产。目前GF的客户正使用7nm设计工具的0.5版,今年晚些时候将更新到PDK V0.9,接近最终版。

要知道GF的大客户在给定制程下,并不需要最终版的PDK才能开发CPU或者GPU,因此GF说的7LP投产计划基本指的就是这些吃螃蟹的 – 大型Fabless半导体制造商(AMD)。

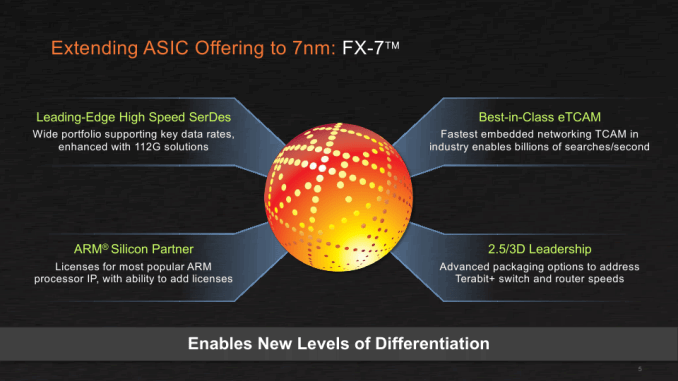

在PDK之外,GF在7LP平台还提供了各种授权:ARM CPU IP,高速SerDes(包括112G),以及2.5D/3D封装选项。对于大客户,GF已经准备好在2018年生产7nm DUV芯片。

本文地址:http://www.moepc.net/?post=2308

Fab 8 7LP已就绪,EUV准备中

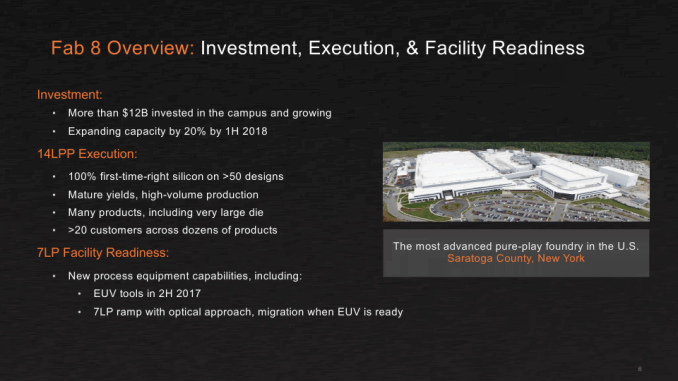

今年早些时候GF宣布要增加Fab 8的产能。目前Fab 8每个月可生产大概60000块晶圆,预计增产完成后可提升20%(14LPP)。

增产没有扩建新建筑,估计是会安装更多性能更好的光刻机。这些新的高性能光刻机也会在7nm DUV大量生产时派上用场。

GF计划在今年下半年给Fab 8安装两套TWINSCAN NXE EUV光刻机。

EUV:解决了很多问题,仍有担忧

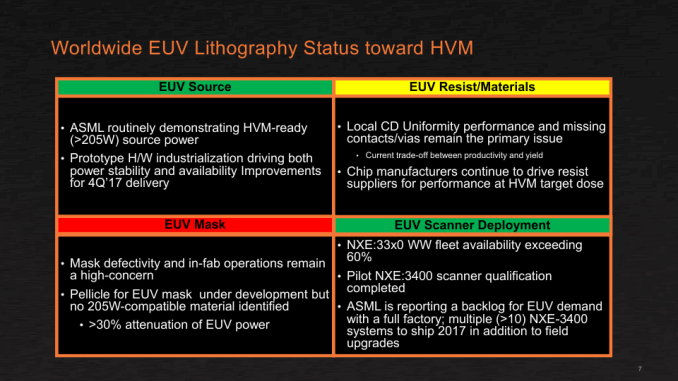

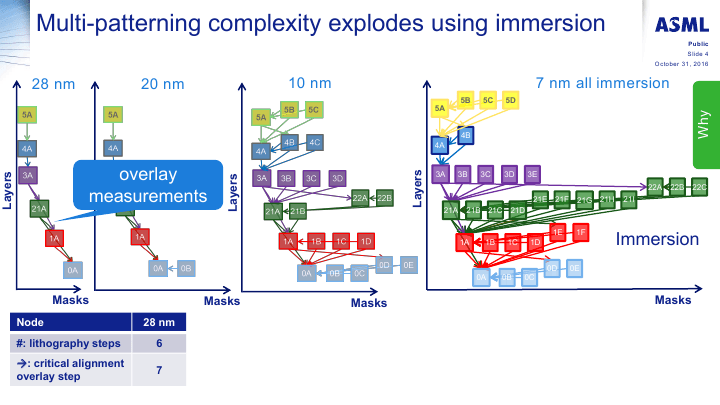

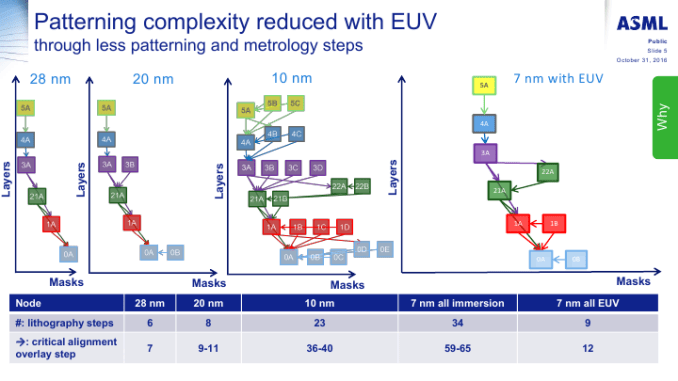

超薄工艺采用的多重图案化(multi-patterning)是业界对13.5nm波长的EUV需求的主要原因。想开发适合大量生产的EUV工具很艰难,最近虽然有了很大突破,但依然还是不大够。这也正是GF在EUV上小心谨慎的原因。

ASML开发了几代EUV光刻机,之前演示用了205W光源。最新的TWINSCAN NXE在更新后要提升60%,对于部署开始阶段已经足矣;预计最终能增加90%,达到DUV水准。

但依然有对EUV的担忧:EUV掩模用的保护膜、光罩瑕疵、以及EUV光刻胶。目前的保护膜的生产率为每小时85块晶圆,比今年计划的125低很多 – 说明目前无法满足大量生产的更强光源。保护膜的瑕疵会影响晶圆,极大降低良率。

Intel演示过的保护膜可以保持200晶圆以上的水平,但不知道什么时候才能用上。

另外强光源需要满足LER线边缘粗糙度和局部临界尺寸的均匀性。

7nm EUV 第一代:提升良率,缩短周期

GF将把EUV应用于特定层,减少多重图案化的使用(如果可能,完全代替四重图案化),提升良率。

关于EUV投产时间,GF没有提供信息,只称准备好了就会投产。不大可能会在2018,比较符合逻辑的预计是至少2019。

该举措很有道理,不仅能够提升良率,还能让GF从中得到EUV大量生产所需的经验。最好的情况下,GF能用7nm EUV生产7nm DUV +多重图案化的芯片设计。然而半导体设计商每年都发布新品,而且EUV在7nm DUV投产后几个季度才能开始,因此首款7nm EUV芯片很可能是新设计。

7nm EUV 第二代:更高晶体管密度以及线边缘粗糙度

第二代7nm EUV将带来更高晶体管密度,更低功耗/更高性能。而第三代7LP可能会引入新的设计规则,提供更高频率/更低功耗/更大面积。

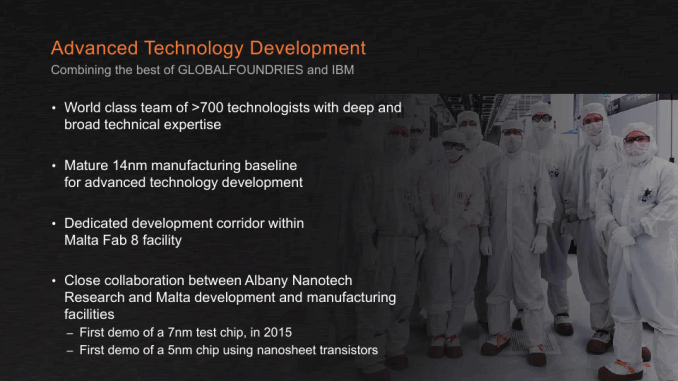

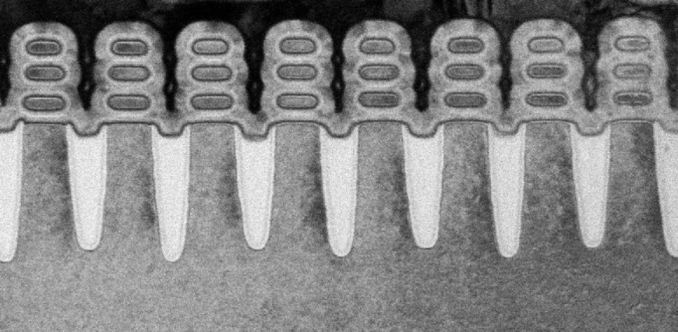

5nm EUV:可调式GAA FET

GAA FET是IBM,GF和三星联合开发的,关键特性是单一制程内可以调整纳米片宽度 – 甚至在同一设计里调整,调校性能。

IBM称相较于10nm制程,5nm能带来40%性能提升(同等功耗),同等频率则能降低75%功耗。

虽然IBM是联合成员之一,但IBM提供的和GF、三星的实际数据不会太一样。

IBM、GF和三星称,GAA FET是通过EUV来调整的。技术上来讲使用DUV设备生产GAA FET是可能的,5nm制程和设计对EUV的依赖度还有待观察。

这仨没人提到5nm大量生产的时间,最早估计会在2021年。

本文地址:http://www.moepc.net/?post=2308

原题地址:http://www.anandtech.com/show/11558/globalfoundries-details-7-nm-plans-three-generations-700-mm-hvm-in-2018

原作者:Anton Shilov

MOEPC.NET编译,有修改,转载请保留出处。

TSMC 5nm(虚标?)这么猛?当初不是把虚标的锅推给棒子吗

明年年底前最多只有zen+,就是14nm-refresh,只要八核能上4.5g就能保证对应咖啡壶不落下风,2018年底到2019年初zen2上线,2020年zen3,酷睿十代冰湖也是同年

@在amd看大门:冰壶更新了什么 还是牙膏?

个人预见:第二代Ryzen 2018年Q1季度发布,使用GF 14nm+工艺;第三代Ryzen 2019年Q1季度发布,使用GF 7nm DUV工艺;第四代Ryzen 2020年Q1季度发布,使用GF 7nm EUV工艺;第五代Ryzen 2021年Q1季度发布,使用GF 7nm EUV+工艺。

@ayu:个人较为保守,ryzen-refresh估计明年早中期能登场;但7nm世代的zen系列怎么说也要等到2019年中后期,7nm世代第一款产品不大可能是cpu,倒有可能是gpu~

这说明gf终于不坑爹了?

@wangbaisen:GF……比你想象的还要坑

说的好。这意味着18年底量产十拿九稳。

即使7nm前期良率低一些,AMD靠IF总线随便互联的设计,也可以获得可以接受的芯片利用率

@wannaknow:你的意思是双CCX 四核?

@CBH:就像现在的R5一样啊,还有可以像EPYC那样4合1,8核8通道的怪物。