半导体封装的未来要看FOWLP与FOPLP

从2016年开始,全球的半导体技术论坛、各研讨会几乎都脱离不了讨论FOWLP (Fan Out Wafer Level Package)这项议题。FOWLP会为整个半导体产业带来如此大的冲击性,莫过于一次就扭转了未来在封装产业上的结构,在在影响了整个封装产业的工艺、设备与相关的材料,也将过去前后段鲜明区别的工艺,将会融合再一起,极有可能如同过去的液晶面板厂与彩色滤光片厂的历史变化,再一次出现重演。

FOWLP (Fan Out Wafer Level Package)顾名思义就是和现有WLP的Fan In有着差异性,最大的特点是在相同的芯片尺寸下,可以做到范围更广的重分布层(Redistribution Layer),基于这样的变化,芯片的脚数也就将会变得更多,使得未来在采用这样技术下所生产的芯片,其功能性将会更加强大,并且将更多的功能整合到单芯片之中,同时也达到了无载板封装、薄型化以及低成本化等等的优点。

使得三星电子败退于A10处理器的FOWLP封装技术

在讨论FOWLP(Fan-Out Wafer Level Packaging)封装技术之前,先简单的说明FOWLP封装技术,若对这些先进技术尚不熟悉的话,也可藉此了解一些关于FOWLP的概廓。

基本上,FOWLP封装技术原本是由德国Infineon Technologies所自行开发出来的封装技术,当初寄望成为新世代封装技术之一而受注目,但是由于种种的关系,使得整体良率过低,因此无法达到普及的程度,但FOWLP并非就此消失,而是深刻的留在各大半导体企业的心中,同时也默默地进行各项改进以及调整。

例如,台积电采用此一技术做为基础,并且加以改进。使得台积电在2016年,全面利用自行所开发的扇出型晶圆级封装(InFO FOWLP ; Integrated Fan Out FOWLP)为APPLE生产封装新一代iPhone 7/7Plus所需的A10处理器。此举备受全球业界的注目,同时刺激了全球各大半导体企业加速了FOWLP封装技术的开发。

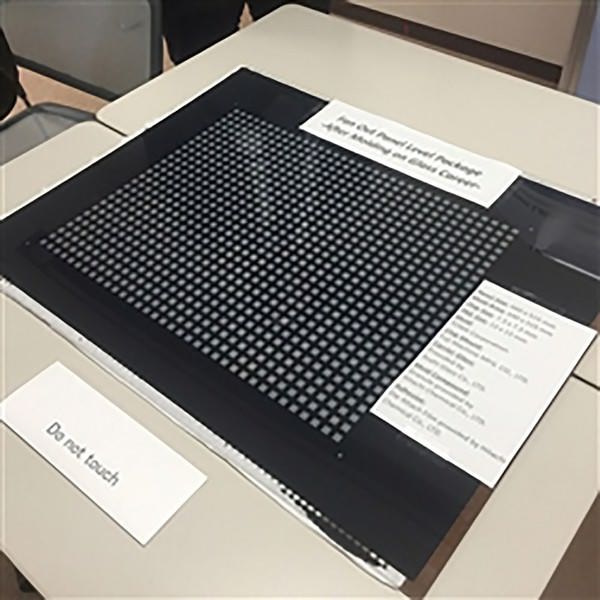

图一 : 采用FOWLP晶圆级封装所生产的A10处理器为台积电抢下APPLE订单

在此之前,Apple针对iPhone所需的处理器是分别透过台积电和三星电子代工生产,然而由于三星电子在FOWLP技术上的开发进度迟缓,并且落后于台积电,因而台积电拿下了Apple在iPhone 7/7Plus所需A10处理器的所有订单。

而三星电子方面,原本对于FOWLP封装技术的态度是相当的消极,这是因为对于目前本身所拥有的层迭封装技术(PoP ; Package on Package)是相当有自信心,自信有能力持续站在领先的地位。但是当因为台积电出现扇出型晶圆级封装技术,而导致痛失APPLE的A10处理器之后,三星电子对于封装技术方面,也出现了研发态度的转变。

首先,三星电子携手其集团旗下的三星电机(SEMCO),以成功开发出面板等级(Panel Level)的FO封装技术-FOPLP(Fan-Out Panel Level Packaging)为首要目标,三星电机(SEMCO)是三星集团下以研发生产机板为主的企业,集团内所有对于载板在技术或材料上的需求,均由三星电机主导开发。虽说如此,尽管三星电子全力研发比FOWLP更进步的“扇出型面板级封装”(Fan-out Panel Level Package、FoPLP),但估计仍需一两年时间才能采用。

图二 : 三星电子全力发展FOPLP工艺技术期望在APPLE的下一代处理器扳回一城

半导体业界关注的FOWLP封装技术究竟为何

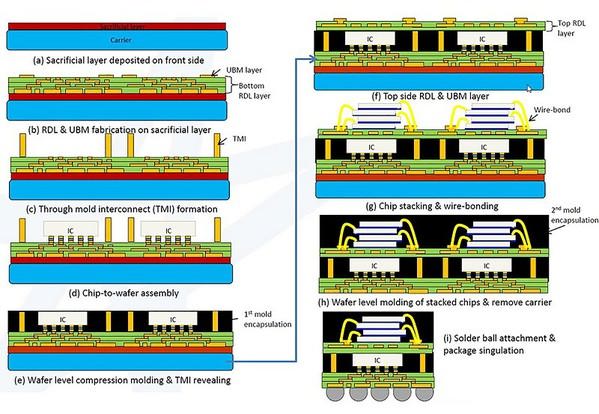

基本上,参考FOWLP封装技术的简略示意图。在晶圆的工艺中,从半导体裸晶的端点上,拉出所需的电路到重分布层(Redistribution Layer),进而形成封装。在这样的基础上就不需要封装载板,更不用打线(Wire)以及凸块(Bump),进而得以降低30%的生产成本,以及减少芯片的厚度。

图三 : 从半导体裸晶的端点上,拉出所需的电路到重分布层进而形成封装,就是所谓的FOWLP封装技术

在芯片中的重分布层会因为缩短电路的长度,使得电气讯号大幅度的提高。在过去,对于WLCSP的半导体芯片面积和封装面积是相同的来比较,FOWLP技术下的芯片的面积比原本封装后面积小很多,因此,可以完成更多脚位设计,或是大大减少封装后半导体芯片的面积,达到小型化芯片的需求。使得原本需要数颗生产成本较高的直通硅晶穿孔(TSV ; Through-Silicon Via),进化到能将不同的组件透过封装技术整合在一起,并且小型化的SiP(System in Package)封装技术。

为了形成重分布层,必须将封装工艺导入晶圆的前段工艺,因此也打破了固有前段工艺与后段工艺藩篱,这对于芯片生产者来说如何完成到一贯性的工艺技术(Full Turnkey)就显得相当重要。在此之下,封装代工业者以及封装载板材料业者或许就会出现是否能继续存活下去的关键问题。因此,对于未来的半导体世界来说,决胜手段已不是仅仅只是在5纳米、3纳米工艺细微化的能力,而是已经延伸到前后段工艺的一贯性的工艺技术。

而在半导体先进工艺技术上落后台积电的三星电子,如果无法追上台积电的话,那么在iPhone的这个订单竞赛中将不会存在任何的机会性。同时在这个商业竞赛中,不仅仅只有芯片代工厂的竞争,同时也是半导体工艺设备以及材料业者间的竞争。

FOWLP到底有多大的市场规模

饱受众人所注目的FOWLP封装技术,虽然得以大幅度简化过去需要复杂工艺的封装工程,但是,在硅晶圆部分(前段工艺),还是必须利用溅镀以及曝光来完成重分布层。到今天为止,在先进的封装工艺技术上无论是从覆晶封装(Flip Chip),还是2.5D/3D领域的直通硅晶穿孔技术,制作困难度都不断的增加,投入成本也一直在增加,因此如果想直接跨入FOWLP封装技术领域,实在很难期望一步就能够达成。

不过虽然如此困难,但各大半导体业者仍旧持续投入大量的研发成本,为的就是期望能早一日进入这一个先进的封装世界。尤其在台积电在利用FOWLP这个封装技术拿下了APPLE所有iPhone 7的A10处理器而受到注目之后,相信未来并不是只有APPLE,而是所有新一代的处理器都将会导入FOWLP这一个封装工艺。

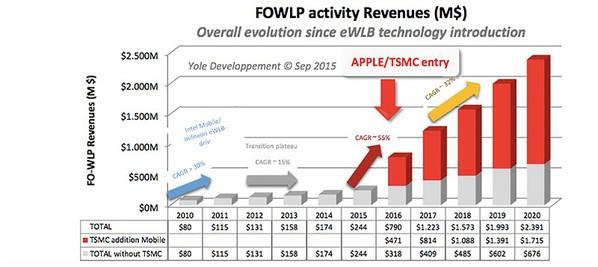

根据市场调查公司的研究,到了2020年将会有超过5亿颗的新一代处理器采用FOWLP封装工艺技术,并且在未来,每一部智能手机内将会使用超过10颗以上采用FOWLP封装工艺技术生产的芯片。市场调查公司相信,在未来数年之内,利用FOWLP封装工艺技术生产的芯片,每年将会以32%的年成长率持续扩大其市场占有,到达2023年时,FOWLP封装工艺技术市场规模相信会超过55亿美元的市场规模,并且将会为相关的半导体设备以及材料领域带来22亿美元以上的市场潜力(图四)。

图四 : 到达2023年时,FOWLP封装工艺技术市场规模将会超过55亿美元

FOPLP可以量产出数倍于300毫米硅晶圆芯片产品

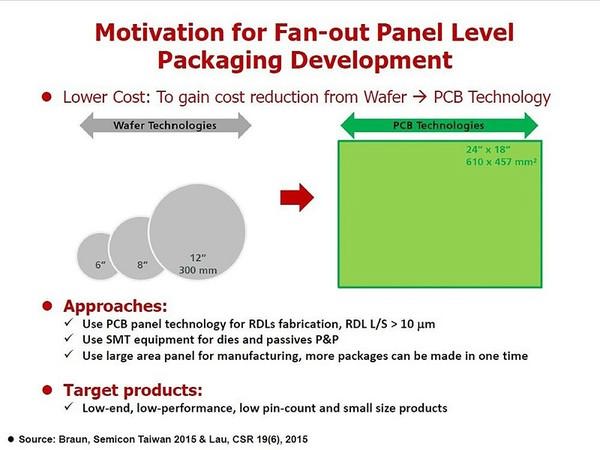

FOPLP封装技术是基于具有整合前后段半导体工艺,FOWLP技术的延伸突破性技术,晶圆工艺上采用FOWLP技术的话,在直径为300毫米(mm)晶圆上的硅裸晶(Silicone Die),可以将前后段工艺整合进行,并且可以将其视为一次的封装工艺,大幅度的降低工艺生产与材料等等的各项成本。

但是如果能够在比300毫米晶圆更大面积的面板(方形面积的载板)上进行FO工艺的话,那么就被称为FOPLP封装技术,这样的技术无论是印刷载板,或者例如是液晶面板用的玻璃载板上,都可以适用。

以目前而言,比300毫米(mm)硅晶圆更大的载板,包括了例如像610mm×457mm印刷载板,和这样的面积相比较,300毫米(mm)硅晶圆的面积约为707mm2,而610mm×457mm却可以达到约2788mm2,这大约是300毫米(mm)硅晶圆的4倍面积,而可以简单的视为在一次的工艺下,就可以量产出4倍于300毫米(mm)硅晶圆的芯片产品(图五)。

图五 : FOPLP在一次610mm×457mm印刷载板的工艺下,就可以量产出4倍于300毫米(mm)硅晶圆的芯片产品

当然如果期望达到在如此高密度下量产时,并且将后段封装工艺整合进去时,那么重分布层(Redistribution Layer)的工艺技术就变得不可或缺。例如,在印刷载板上使用FOPLP技术,不仅仅考验着印刷载板的工艺能力,特别在高密度的布线结构时,所需要的增层(Buildup)布线工程,就必须仰赖重分布层(Redistribution Layer)的完成。以目前来说,线距大多是在10微米(μm)以上,但是一但进入到了晶圆等级FOWLP技术的工艺时,重分布层的密度就会比一般更高,这时线距大多便成了是5微米(μm)以下。

材料供应商需调整其研发方向,才可持续地扮演关键性的地位

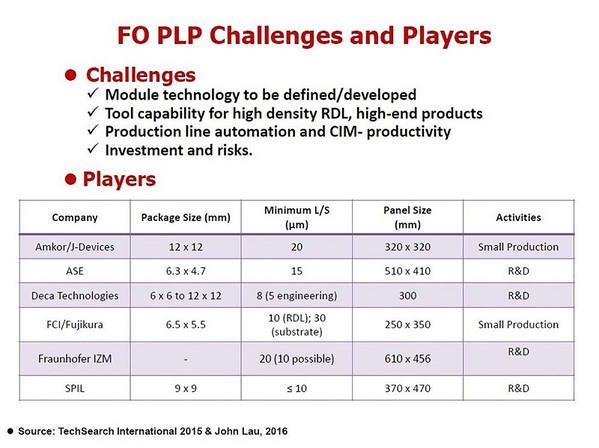

目前积极投入FOPLP工艺技术的半导体企业包括了,三星电子、J-DEVICES、FUJIKURA、日月光(ASE ;Advanced Semiconductor Engineering)、DECA TECHNOLOGIES、 SPIL(Siliconware Precision Industries)..等等(图六)。

图六 : 全球各大封装业者均积极投入FOPLP工艺技术

业界也有人猜想,三星电子相当有可能重新修改较旧的LCD溅镀、曝光等等的设备,来进行FOLPL的封装工艺,由于能够达到更大面积的生产,一般认为这样的面积下量产出来的芯片成本,或许将会比台积电更低更具竞争力。藉由和集团的三星电机合作,共同面对台积电的竞争,来争夺APPLE的下一代处理器机会。

面对半导体工艺技术不断的革新与整合,使得使用载板的封装比例逐渐呈现减少的趋势,根据市场研究机构的统计,载板的封装比例已经由2010年的51%降低到2015年的39%。而不需使用载板的晶圆级的封装比例,则是由2010年的2%大幅度的攀升至2015年的26.7%。

因此,伴随着半导体量产与封装技术的演进,原本是扮演着不可或缺角色的封装材料供应商(包括载板),也逐渐在技术演进的下,市场将急速的萎缩。此时,封装材料供应商需调整其研发方向,并逐渐向前段工艺跨进以及布局,才可在技术急遽演进的潮流中,持续地扮演关键性的地位。

via:ctimes

上淘宝搜芯片打磨机,就能看打磨a芯片的cnc。。。

里面还真是要磨两层,磨掉第一层的时候就有bga。

之后再磨一层才是pbc底板。

arm芯片发热这么低吗?