【STH】AMD Naples服务器实物及结构图曝光

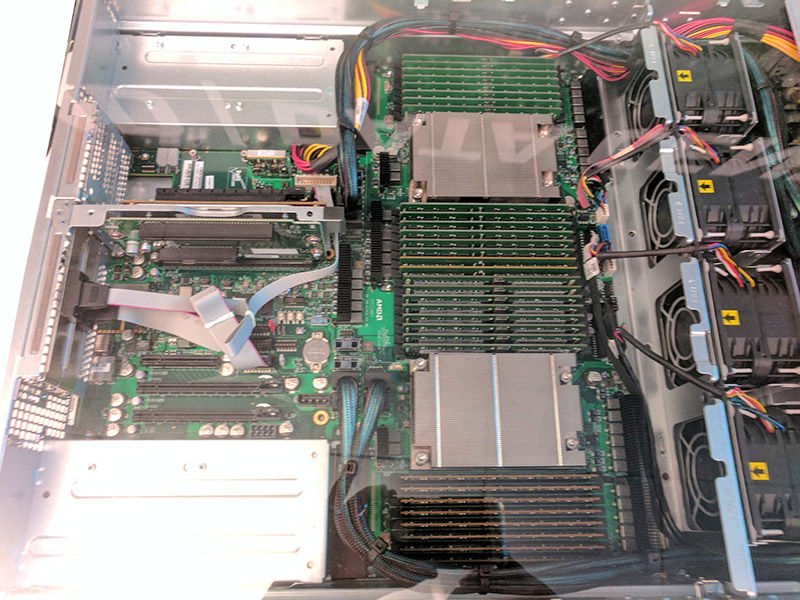

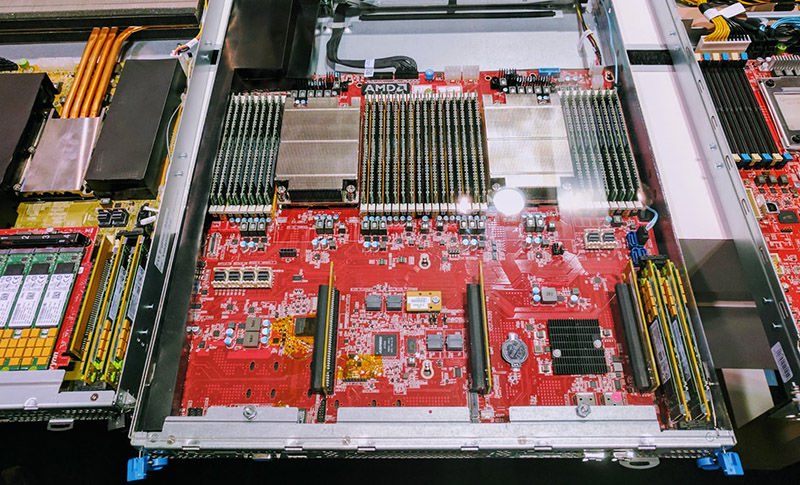

2017年OCP峰会上曝光了AMD x86 2P服务器平台,代号Naples的实物图。

之前Ryzen Tech Day曝光的首个Naples平台为AMD Speedway系统

而在OCP峰会2017上,微软和AMD展示了Project Olympus的成果 – AMD Naple服务器

右边的是高通的Centriq2400,左边是尚未发布的Intel CPU(例如Project Olympus的Skylake-EP/Purley服务器)

Naples有几个PCIe X16插槽,SFF PCIe接口,还有给m.2 NVMe SSD留下的很大空间。

32个内存槽,每插槽8通道DDR4带来了高于Intel Purley的带宽。

PCB中间有一个ASPEED(信?科技)的BMC。虽然Naples已经是SoC设计,但外部BMC依然是系统的一部分。

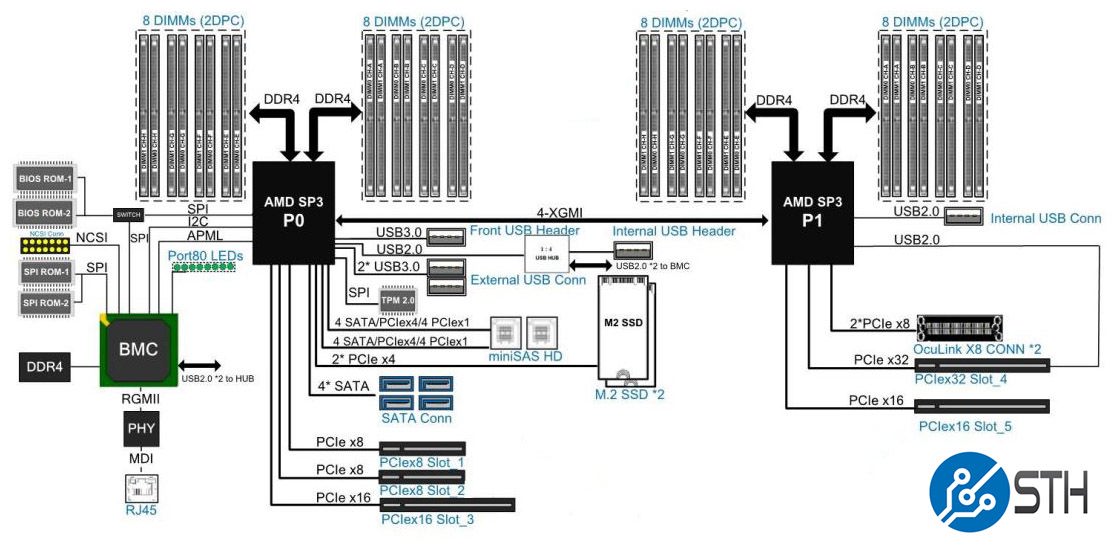

Naples 2P服务器结构图

STH从AMD获取了Naples双路服务器的结构图【这图实际早就有了】。

不同的服务器接口和插槽配置不一样,这只是一个例子。

每路16内存插槽,双路就有32个DDR4插槽。

AMD称Naples有128条PCIe 3.0供I/O使用,在这里的配置显示,16条供给高速I/O,剩下112条供PCIe拓展设备使用

双路Naples在USB、BMC和其他部分用上高速I/O后,依然还能剩下112条PCIe 3.0。这112条PCIe 3.0可供PCIe显卡、NVMe SSD等使用。

还可以看到CPU之间的4xGMI连接。Naples双路上每颗CPU都有128条PCIe 3.0,但其中64条供给CPU之间的通信。

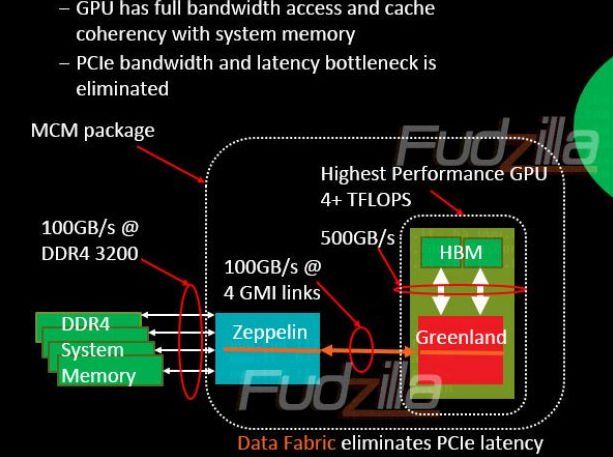

一年前的老图

目前的E5 V4单路有40条,双路有80条PCIe,一般配置72条左右。

而Naples单路128条,双路128条,实际可供拓展112条,依然要多出40%。

来源:STH,本站整理翻译,转载请注明出处。