难以忽视的真相:Intel Larrabee的背后故事【Part1】

译者前言:这篇文章写于09年10月,也就是Larrabee计划中止前7个月。虽然原文用词有点偏讽刺,但说的基本都是事实。

8年后再来看这篇文章,能发现不少让你感到恍然大悟的地方。?Marvin

当Intel宣布其正在开发下代显示芯片?Larrabee时,几乎每个人都认为Intel能够轻松抹杀ATI/NVIDIA。毕竟Intel用Core酷睿架构打的AMD措手不及,此时正感到无比安全。

近几年我一直都在关注Larrabee计划,并和众多Intel员工有过各种公开或秘密的讨论。随着时间推移,在远方闪烁着的亮点渐渐变成了挡在我们面前的警示灯。在和Intel工程师、业界分析师等交流过IDF论坛和Larrabee DEMO的内容后,回头已经没有意义。

这篇文章总结了我们关于Larrabee的信息,包含几百个e-mail和聊天、许多路线图和秘密讨论。当我们向Intel的PR询问Larrabee时,他评论:”你们的故事纯属无稽之谈,和事实毫不相干。”,还说我们的消息来源“是坨屎” – 而这正指的是Intel自己。我们看重日后的一些评价,例如一场会议后的评论:“since [Intel] PR claims we don’t work on LRB, this is a blue cookie”。当然也有对我们自身真实性的怀疑,但在这里我们会一如既往地揭露信息,无论是好是坏。我们希望都是好消息,但即便是坏消息,我们也不会坐视不管。

不幸的是对于PR、营销和销售部门来说,每个企业都要依赖一群对产品倾注心血的工程师,如果没有他们,就不会有你手上堆积着成百上十亿晶体管的芯片。工程师们说的话并不生涩难懂 – 实际上他们都很欢迎交流。

这被我们称之为,一个难以忽视的真相。

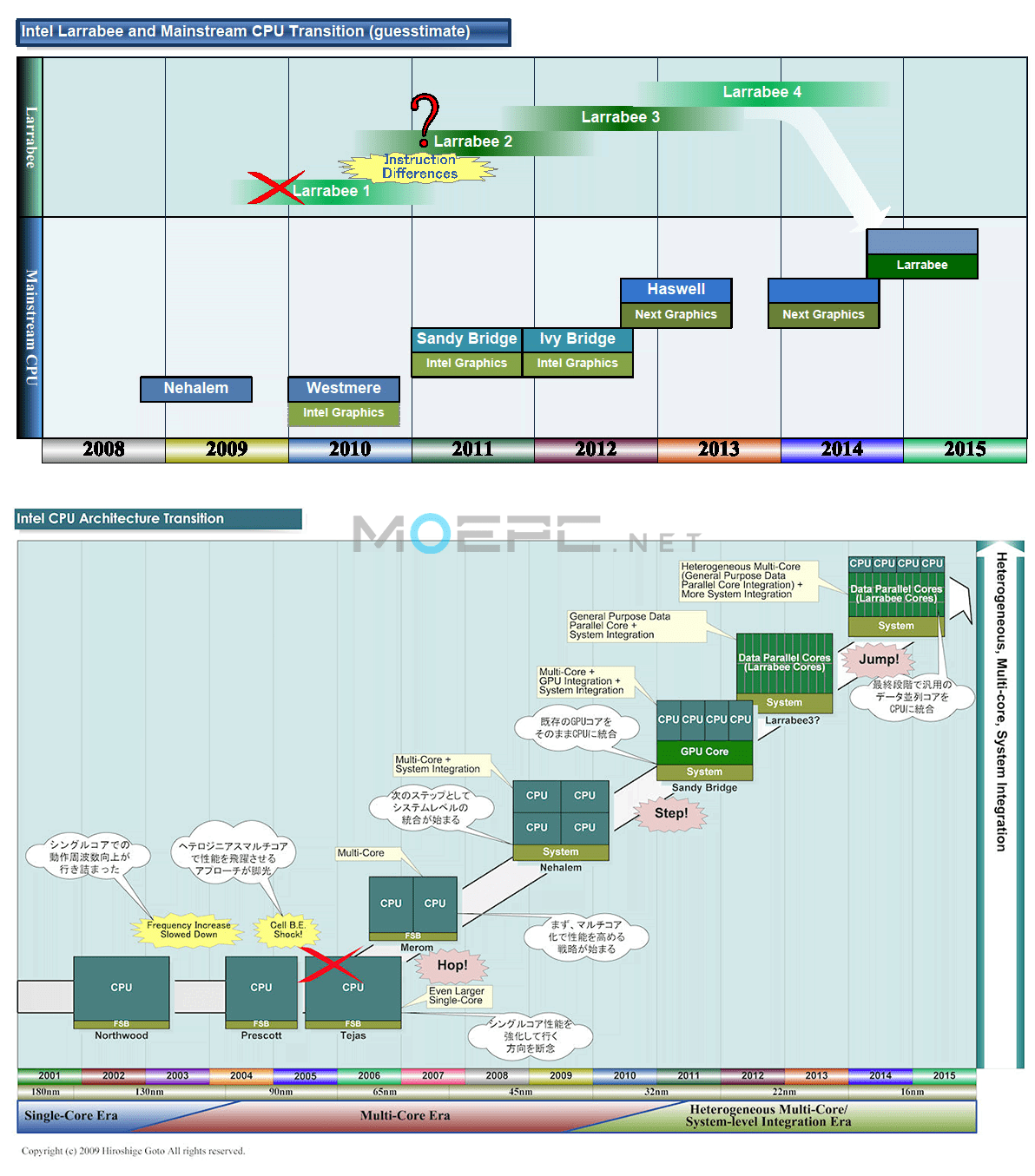

对于Intel这么大的公司,Larrabee计划的发展不应该落到这个下场。实际上按照这么多年收集到的信息,Larrabee一点都不像是Intel的项目*1。我们在过去几年看到的曝光信息令我们感到震惊:在各种场合,我们看到过内部路线图,听他们抱怨管理层不切实际的预期。首先是发布日期:Intel内部路线图起初写着“2008年出样”,然后”2008年Q4发布”、“2009年发布”。到2008年夏天为止,我们还看到“2009年中”、“2009年下半年”改成了“2010年”、“2010年下半年”。近期和几个工程师交流时他们说:“我们还需要13-18个月才能完成Larrabee”,到了讲故事的时间。

通向Larrabee之路

在Intel准备开始项目前,Larrabee就已在各方面存在诸多问题。Intel预谋Larrabee很多年,但当时这家以CPU为中心的公司沉迷于打造10GHz的奔腾4*2,觉得它也有足够的计算能力来驱动显示。这和当时采用IBM Cell处理器的索尼想法一致 – 原本PS3想集成2颗4GHz的Cell CPU。在想法破灭后,则由NVIDIA接下了这烫手山芋:要在发布前不到12个月内给PS3打造GPU。而并不好说Imagination能挽救Larrabee。

和频率只达到3.2GHz且问题一堆的Cell一样,Intel内部关于Tejas也有过争论*3,并带来了很大震动 – 即便是Intel内部顽固派也认识到NetBurst架构变成了NetBust,转而拥抱曾开发奔腾M的Israeli队伍*4。在这期间曾听到一个口号“Megahertz is Megahurtzing us”*5,经常出现在针对当时大热门 – AMD Opteron皓龙的销售讨论里。还有个关于当时Intel内部权力斗争的故事,这个留到以后。我想说的是,因为某种原因部分管理层突然开始极力推动Larrabee计划。

CPU方面,Intel在完成酷睿架构后,十分确信它将使Intel转型为真正基于产品的平台公司,而不是仅基于PPT。Intel每年给Imagination大量授权费用,在低端上网本/笔记本芯片组里集成了“低能耗、低性能”的PowerVR – 对于Intel这种出货量上亿的顶级ASIC设计公司的确有点搞笑。

但与很多人想象的不同,PowerVR的性能低下并不仅仅是Imagination的错。主要问题是:Intel请了第三方“Tungsten Graphics”*6来写GMA的驱动。驱动问题的本质在于“GMA500的性能严重受到狗屎驱动的影响。Intel没有买Imagination的SGX系列驱动,却请Tungsten Graphics去写驱动。尽管Imagination这边向Intel多次提出反对,Tungsten写的驱动还是没有使用芯片内置的固件,而是强制分配给软件 – CPU来处理顶点。”这也就是为什么“狗屎Intel集显”的原因并不全在硬件,更大程度上在于Intel有问题的决策。记得当时Intel就用这玩意演示过酷睿2双核和四核之间的性能差异,问题是 – 演示是一码事,转嫁给消费者就是另一码事了。

其次,Intel用的是PowerVR SGX535,和iPhone、诺基亚N900、索尼爱立信XPERIA等智能手机一样。如果Intel用了SGX545,上网本/笔记本*7就能完爆老的GenX架构集显。

硬件性能不足、狗屎驱动导致Intel总是被游戏开发者嘲笑,如果出版商强制游戏支持Intel集显则会上升到厌恶的程度 – 导致Intel同时拥有最好的CPU和最烂的GPU这一矛盾[几个重要开发者提醒说:写游戏的时候从没把GMA当成“GPU”]。事实上准备这篇故事时Tech Report就爆出GMA集显和驱动对3DMark Vantage优化的事件。Epic Games的Tim Sweeney[虚幻引擎]不留情面地评论说:“Intel集显无法使用。任何时候都一样”。不过这则评论相比下面这条已经算“礼貌”了:“Intel总是说:‘噢,我们知道以前没法使用,但下代…’ 总是说下一代能用。现在一代又一代,却从没有过任何提升”。

Intel有对开发者提供支持,比如Tim Sweeney正全力开发的虚幻4引擎将首先支持Larrabee…..当Larrabee完成时。当然也有对AMD/NV的直接硬件支持,Fermi架构支持原生C++代码执行。但这是另一码事…

Larrabee的概念大概在2005年左右成熟。Intel开始在全球各地招人,尤其是俄勒冈、加利福尼亚和德国。想设计一颗高度复杂的芯片,就需要依靠数支队伍在不同层面的分工,这也可能是造成目前Larrabee计划现状,以及路线图推迟了两年多还可能继续往后推的原因。

“CPU比GPU更容易设计”

首先,设计一颗GPU是非常艰难的过程。甚至有些怀疑者会说:“只用设计一个流处理器然后直接暴力堆积就行了”,这完全是瞎扯淡。今天的GPU都是极度并行化的猛兽,它们依靠两样东西:驱动程序以及极度并行化的硬件。这是ATI/NV/Intel的工程师都证实了的。

ATI和NV的DX11 GPU在微架构级别就支持大指令宽度,设计这样的芯片是非常困难的。GPU和CPU在计算规模上完全不同。CPU为随机任务所优化,因为CPU并不知道接下来将要计算什么;而驱动已经为GPU做了大部分工作,只把成百上千条指令排好队列等着执行。因此CPU需要大量缓存;而GPU并不需要[除非你要GPU做计算用途]。

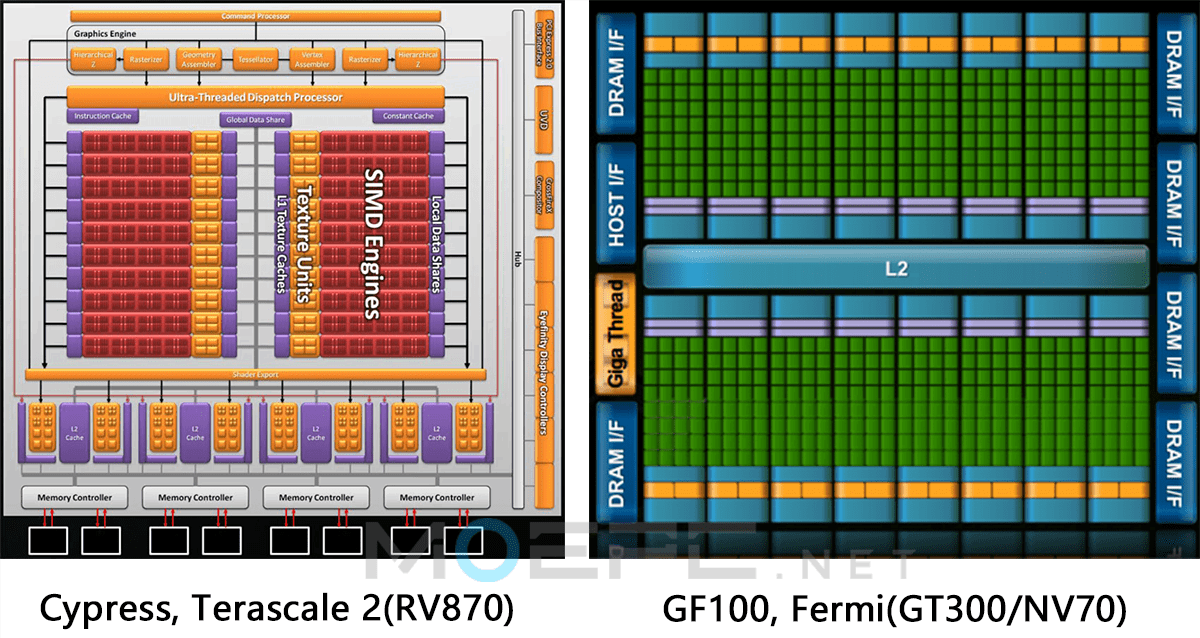

ATI RV870,也就是Cypress 以及NV的 GT300 Fermi – 原版Larrabee的对手

Intel Larrabee的设计目标是与这俩竞争,尤其是右边那个。

ATI和NV都朝着同一方向前进,开发极度并行的架构,GPU的缓存和带宽也在增加。比如ATI的HD5870配有160KB L1缓存、160KB的Scratch缓存以及512KB 的L2缓存。L1带宽大概在1TB/s,L2则为~435GB/s,这比目前的任何CPU缓存都要强,况且Cypress的运行频率还”只有”850MHz。预超频的950MHz版本L1能达到1.1TB/s,L2带宽也有500GB/s。要知道这是颗40nm制程的芯片。

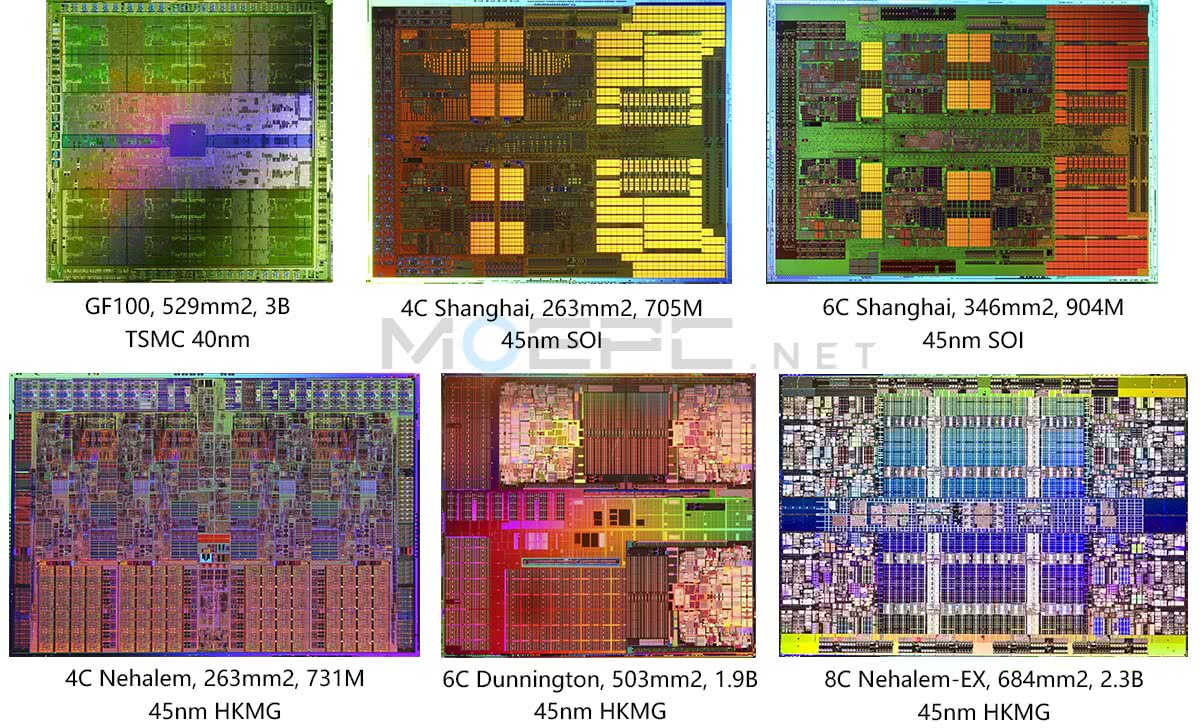

另一方面,NVIDIA最近发布的Fermi架构,将会出现在GT300/NV70/GF100芯片上。Fermi作为计算GPU架构,拥有1MB的L1缓存和768KB的L2缓存。1MB的L1容量比目前所有CPU都要高:

AMD 四核 Shanghai = 512KB L1 [每核心64KB 指令 + 64KB 数据缓存]

AMD 六核 Shanghai = 640KB L1 [每核心64KB 指令 + 64KB 数据缓存]

Intel 四核 Nehalem = 256KB L1 [每核心32KB指令 + 32KB 数据缓存]

Intel 六核 Dunnington *9= 96KB L1 [每核心16KB 指令 + 16KB 数据缓存]

Intel 八核 Nehalem-EX = 512KB L1 [每核心32KB指令 + 32KB 数据缓存]

此外,Fermi架构的SM包含32个可执行融合乘加[FMA]的CUDA核心,能处理整数或浮点指令。相比之下,Intel会在作为计算GPU的Larrabee上支持FMA,也会在2012年的Haswell架构上支持FMA。(虽然我们现在知道Haswell是在2013..)

那么GPU听起来容易做吗?如果容易的话,GPU公司就不会从本世纪初将近80家变成现在的8家*8了 – 其中还只有两家大量出货桌面和移动版独立GPU,两家在便携设备上大量授权。即便拥有50%GPU市场份额,我们也没把Intel当做消费级”GPU”厂商,因为性能太?了。问问微软有多少Intel硬件在验证过程中被放弃过*10。我们知道实际数字,可以确定的说结果并不光彩。

所以Intel知道应该做什么 – 不然就可能在不断视觉化的世界中被潮流抛在后面。Intel知道打造Larrabee很难。问题是他们那套陈旧的思考方式低估了这样一个计划所需的人力物力和时间。

AMD的对策:和NVIDIA合并 – 一桩未成的婚事

面对Intel同时开发CPU、cGPU以及将来的二合一,AMD的反应很简单:Hector J. Ruiz及其执行团队开始讨论与NVIDIA的整合,最后定在2005年下半年。当时的SNAP战略性合作*11使得AMD与NVIDIA都很清楚各自的底细。谈了几个星期之后没成*12,AMD开始考虑买下ATI,最终数月后宣布收购[2006年7月]。

如果AMD和NV整合成功,现在的ION芯片组应该就会是MCM了,上网本的格局也会大有不同[写文章的时候上网本很流行]。但AMD选择了更保守的ATI,现在AMD的策略取得了回报。

关于ATI的收购是否溢价过多的问题,可以把Intel打造Larrabee的代价当做一劳永逸的回答。关于Larrabee的花费,近几年听到过各种预测,几乎每个都超过10亿美元。最高的是”我们烧掉了30亿美元”,这依旧还是推测。数字并非来自于会计师,Intel花了多少依旧无法计算。

Intel Larrabee 规格

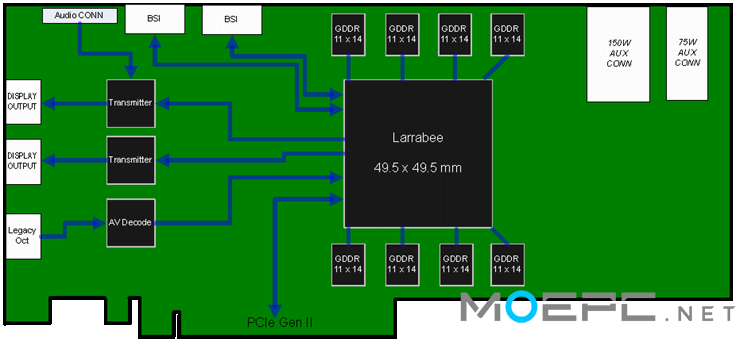

Intel Larrabee的早期PCB布局 – 目前的版本也没多少改动

Larrabee的设计目标:打造一款频率2GHz,16核,2-4MB L2缓存,TDP 150W的芯片。Larrabee将使用成熟的45nm工艺制造。实际上正因为45nm工艺成本已经收回,有富余产量,才没有那么多吹毛求疵的人。即便如此。单芯片(包括封装)成本也有80美元左右。

内存控制器类似于ATI R600:“1024bit”内部环形总线[双向512bit],带宽超过1TB/s,连接着8个64bit 内存控制器[512bit],1GB 4Gbps GDDR5显存,外部带宽256GB/s。结果后来显存带宽变成开发过程中的一大问题。

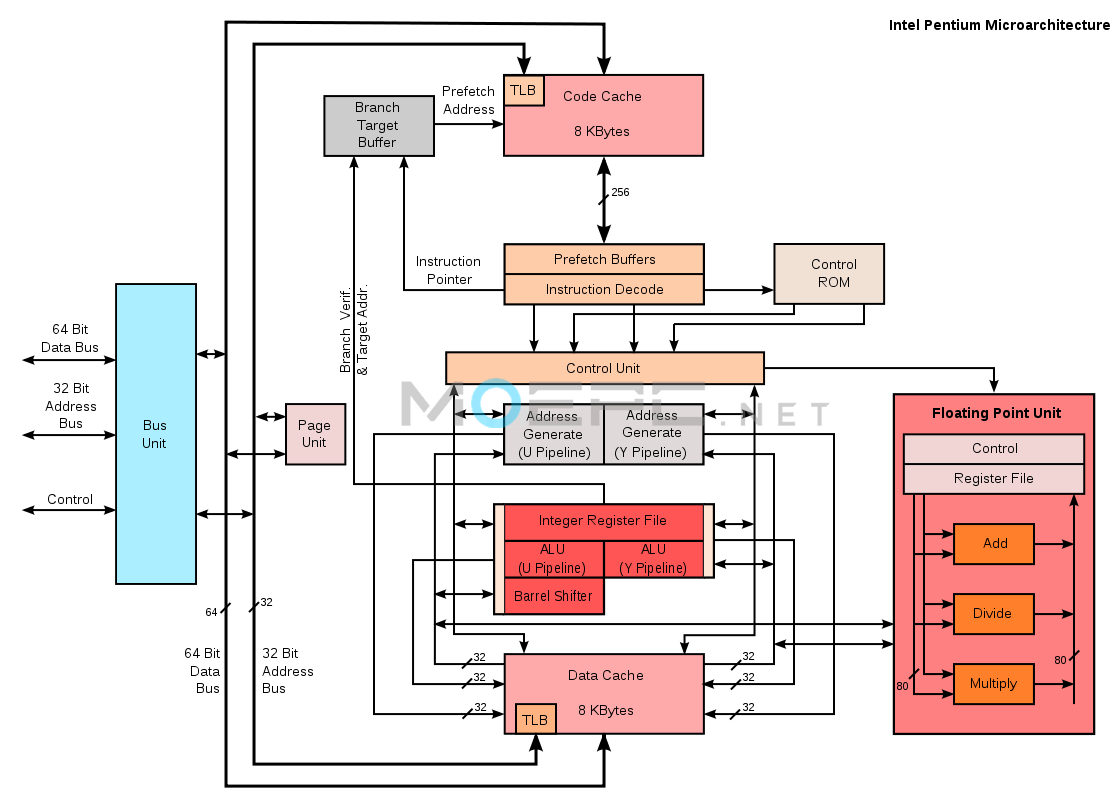

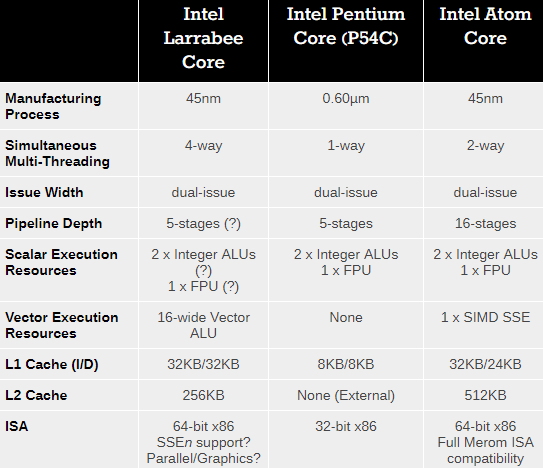

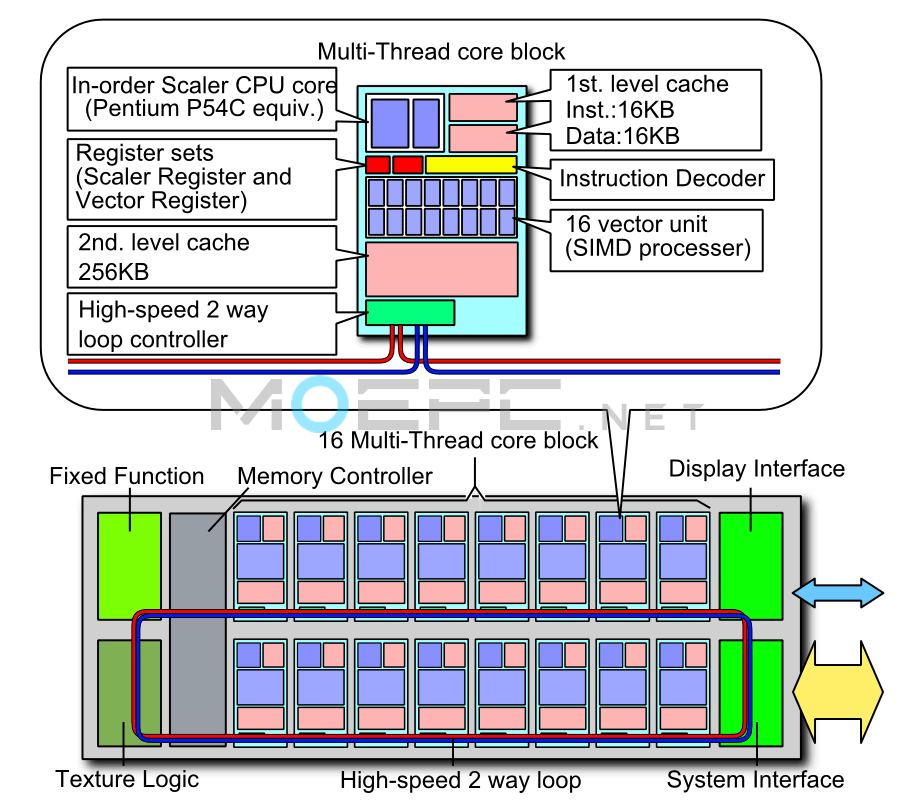

Intel Pentium Architecture

Larrabee与Pentium核心 图源PCWATCH

表格来源Anandtech

执行核心为顺序执行x86,可以同时执行4个线程。它是经过改进的Pentium MMX核心[P55c]的私生子,但为顺序执行。由16-wide SIMD单元负责最繁重的工作,可执行16条 32bit[512bit] AVX指令。为了让一切正常工作并避免闲置,使用上面的环形总线连接16个核心。Larrabee核心拥有64KB L1缓存[32KB数据+32KB指令],与Nehalem相同。性能模拟显示,16颗x86核心+AVX指令无法达到2008-2009年ATI和NV的主流GPU水平,所以路线图拓展出24、32、48核心的计划,L2依然维持256KB每核心。32核的Larrabee cGPU将有8MB缓存,48核版本达到12MB。24核版本也是8MB缓存,但不知道8MB是否能为所有核心所用,还是每核只有256KB。按照我们的消息来源,“L2缓存大小不成问题。SRAM缓存密度方面我们是众所周知的业界标杆,我们想放多少放多少。在这个方面我们无人能及。”

Intel Larrabee在高端的计划:用Haswell+Larrabee核心抢占HPC市场

当时Intel计划用16核达到1TFLOPS算力,却无法达成目标,就把最低端型号核心数增加了50%。24核和32核型号计划使用45nm制程生产,而48核版本会使用32nm。注意24核版本其实是由32核屏蔽而来。

而8核以及16核版本会作为架构改进的一部分,集成进Haswell架构*13 – AMD就会玩完了。

这是当时的计划。现在来看看Larrabee是如何翻车的,以及现在的情况。

Larrabee出了问题?在2007年?

在2006年首次出现翻车的迹象。我们正与开发Larrabee的不同团队的人讨论,然后收到一封邮件写着“布伦瑞克的团队简直就是一群蠢猪,不应该让他们来开发Larrabee!办公室里的企业文化完全搞坏了。”

如果只是个别抱有不满的工程师,我们自然会不理他。但随着时间流逝,我们收到了各种零零碎碎的更令人担心的内容。在2007年Larrabee开始成形时,我们从团队里进出的人那里听到了令人很担忧的言论。最令人不安的是内存控制器的问题 – “设计高性能内存控制器的这帮人连最基本的管线概念都不懂,还不知道怎么读内存规格。这太荒谬了。”

要知道当时所选用的GDDR5显存在技术层面改动很多,所以比起GDDR3/GDDR4的控制器,Larrabee的控制器必须大改。GDDR5显存与前几代不同 – GDDR3/GDDR4均基于DDR2内存标准,而GDDR5则走了不同路线,与传统DDR3内存也只有一些相似之处。

另外我们一直都保持着与参加Larrabee及其周边计划的各种人员的联系。和Larrabee工程师们一同乘坐长途航班也帮了大忙。这些工程师在传统的美国→德国→印度路线上跋涉,听听他们的想法和担忧很有趣。实际上更主要的还是担忧。当时Intel正处在各种反垄断之类调查的压力之下,与他们签了合同的人们也开始感到不自在。例如:

“唯一能让这些替罪羊,也就是Intel德国雇员(合同工)保持沉默的,是Intel付给的惊人工资 – 大概在每年15-20万左右,包含和internationaltaxsolutions.com签约的德国避税服务。”

当我们收到上面这封邮件时,联系了几位当时以及曾今的Intel合同工,看了邮件之后得到确认,这样的交易确实存在,他们甚至还给我们看了来自美国的几份合同。不用说,当时形势变得非常复杂。

此后我们与许多Intel工程师进行了邮件和语音交谈,此时他们还坚信他们的宝贝Larrabee将有重见天日的那一天。但闭口不谈性能,说什么“我们得先把产品弄出来。第一代该打造生态系统不是?” ,什么“我们需要从第一代中吸取教训,然后打造世界一流的第二代产品”之类。另一个来源还辩解说:“第一代概念验证,第二代对验证结果进行修正,第三代才是真家伙。”

自然而然地,在开发的这个阶段,我们被告知实体芯片会在2010年初到来。然而在旧金山的IDF2007上,某位Intel主管在和几个媒体和分析师闲聊时说漏了嘴:“我们将在2009年5月出货一款32nm 双核CPU + 45nm Larrabee晶片的处理器。”

我们听说后询问了内部消息来源的看法,史无前例地,Larrabee团队发来了一连串邮件,这除了恐慌还能是什么。我们原以为那个主管可能搞错了时间,提前了一年,但这也被”不,那得到2012年”的声明否定了。那名主管不小心说漏嘴也是导致Larrabee计划进展信息的大量泄露的原因之一。

回到Larrabee上来,在过去一年半的某个时间点,工程师们觉得双向512bit环形总线无法喂饱这么多核心,就打算采用多个路径,每个环形总线上8-16核心。这个想法打一开始就很糟糕,幸运的是它没有成真。但开发芯片已经到了这么晚的阶段,还在纠结最基本的芯片组成,实在让人感觉麻烦大了。32核芯片曾经[现在也是]有很多问题,比如缓存一致性问题、喂不饱核心之类。总体来讲Larrabee是一团糟。即便是ATI和NV以前最差的时候*14也远不及Larrabee的程度。

我们一直有听到Larrabee计划的各种问题,但几乎100%的消息都来自于ATI或者NV,所以我们自然会把这类指责归类于典型的FUD*15。但这与后面发生的事情无关。

后面还会有Part2….耐心等待…可能会坑很久

所有图片都是我后来整理的,原图已经找不到了…

MOEPC.NET编译,转载请注明出处。

============17/09/04============

17/11/21:Part2 已更新:

难以忽视的真相:Intel Larrabee的背后故事【Part2】

http://www.moepc.net/?post=2866

核心是英特尔不好好写GPU驱动。

GPU不同于CPU,是被动的。

用于渲染的时候,需要CPU安排好工作,调度的好性能才好。否则各个计算单元相互等待,效率会低。

另一方面,显存带宽很重要,英特尔的集成显卡性能不好,很多时候,是因为不能阻塞CPU使用内存的决定导致的。

一直以来CPU架构设计要比GPU难得多

有幾個圖是Wikipedia zh的圖(圖的原始來源見各圖的描述頁):https://zh.wikipedia.org/wiki/Intel_Larrabee。不過這條目也不是寫得很好

以前的larrabee和现在Intel的knight landing(phi)有什么关系吗?

@aristomarc:LRB死了

Knights Ferry活了

这在Part2里会讲

有的资料不好找

而且坑太多没时间填

注!明!出!处!和!作!者!

一方面去婊其他科技媒体没节操,另一方面不严于律己,啧。

@ssnitrousoxide:注明在Part2的脚注,谢谢。我翻译都还没写完。

不要一上来就开喷。

更不要以恶意来揣度别人。

@剧毒术士马文:他的语气不好,不过我也建议在Part 1文章最后补充一下来源。这样要看原文对照也比较容易找到。

@我土鳖我自豪:内容我都没整理完

@剧毒术士马文:您看这样如何?先在Part 1最后加上原文链接和作者姓名,然后待剩余内容完成后,直接附在Part 1的最后,再把标题里的Part 1去掉重新置顶。

敲碗等更新!

上初中那时候Larrabee吹的上天了,然后现在变Phi

马先生有没有AGESA 1.0.0.7 的文章

我要被内存折磨成大头儿子了

@黄仁旭:1007相对1006改动不是很大

@剧毒术士马文:CR2下的海力士单面已经不如鸡

似乎Tungsten Graphics现在还在给牙膏厂写Linux驱动啊?

@轮子妈:gg

国际著名A炮—马文先生

@smtdbd:总不能翻译A炮文章就是A炮吧,当然马先生的决定权也是很重要的。

@黄仁勋:怕是钦点的A炮

要是AMD真的和nVidia整合了……我突然一阵恐惧

@我土鳖我自豪:当时amd真的从ati和nv中选择,但是老黄一定要当老大,amd就买了ati

@janzizak:老黄当老大其实没错,不管n家行销策略多么不可描述(负优化),但是老黄的战略眼光真的可以说是半导体业界最强,很早就意识到了显卡在今后超算领域的重要性搞出了cuda和tesla,然后又预见到超算重心转移到神经网路果断抛弃了双精度,能耗比的努力最终做到了桌面u塞笔记本。。。。。

@appleache:同显卡不同时期驱动的实际性能并没有显示出持续性下跌,大部分是上下浮动,只能说这年头N卡驱动更新后需要hotfix的频率越来越高

@搞事情:我说的负优化主要是指hairwork,cuda和gameworks这类就是要故意恶心对方的